(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

### <u>MODEL ANSWER</u> WINTER– 18 EXAMINATION

**Subject Title:** Digital Techniques

**Subject Code:**

22320

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q.N. | Answer                                                                 | Marking<br>Scheme |

|-----------|-------------|------------------------------------------------------------------------|-------------------|

| Q.1       |             | Attempt any FIVE of the following:                                     | Total Marks<br>10 |

|           | a)          | Write the radix of binary,octal,decimal and hexadecimal number system. | 2M                |

|           | Ans:        | Radix of: Binary – 2                                                   | ½ M each          |

|           |             | Octal - 8                                                              |                   |

|           |             | Decimal - 10                                                           |                   |

|           |             | Hexadecimal -16                                                        |                   |

|           | b)          | Draw the circuit diagram for AND and OR gates using diodes.            | 2M                |

|           | Ans:        |                                                                        | 1 M each          |

|           |             | <b>Diode AND gate : Diode OR gate :</b>                                |                   |

|           |             | $ \begin{array}{c}                                     $               |                   |

| c)         | Write simple example of Boolean expression for SOP and POS.                                                                                                 | 2M                              |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|

| Ans:       | SOP form:                                                                                                                                                   | 1 M each<br>(any proper         |  |  |  |

|            | $Y = AB + BC + A\overline{C}$                                                                                                                               | be considered)                  |  |  |  |

|            | POS form:                                                                                                                                                   | considered)                     |  |  |  |

|            | $Y = (A + B) (B + C) (A + \overline{C})$                                                                                                                    |                                 |  |  |  |

| <b>d</b> ) | State the necessity of multiplexer.                                                                                                                         | 2M                              |  |  |  |

| Ans:       | Necessity of Multiplexer:                                                                                                                                   | 235/                            |  |  |  |

|            | • It reduces the number of wires required to pass data from source to destination.                                                                          | 2 M(any tw<br>proper<br>points) |  |  |  |

|            | For minimizing the hardware circuit.                                                                                                                        |                                 |  |  |  |

|            | For simplifying logic design.                                                                                                                               |                                 |  |  |  |

|            | • In most digital circuits, many signals or channels are to be transmitted, and then it becomes necessary to send the data on a single line simultaneously. |                                 |  |  |  |

|            | <ul> <li>Reduces the cost as sending many signals separately is expensive and<br/>requires more wires to send.</li> </ul>                                   |                                 |  |  |  |

| e)         | Draw logic diagram of T flip-flop and give its truth table.                                                                                                 | 2M                              |  |  |  |

| Ans:       | Note: Diagram Using logic gates with proper connection also can be                                                                                          | 1M (any on                      |  |  |  |

|            | consider. Logic Diagram:                                                                                                                                    | diagram)                        |  |  |  |

|            | $\stackrel{\circ}{\downarrow}^{Pr}$                                                                                                                         |                                 |  |  |  |

|            | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                       |                                 |  |  |  |

|            | $\bar{Q}$ $\bar{Q}$                                                                                                                                         | 1 M                             |  |  |  |

|            |                                                                                                                                                             | •                               |  |  |  |

|            | OR $OR$                                                                                                                                                     |                                 |  |  |  |

|            |           | Input<br>T <sub>n</sub> |            | Output<br>Q <sub>n+1</sub>   | <b>Operation Performed</b>                          |                  |

|------------|-----------|-------------------------|------------|------------------------------|-----------------------------------------------------|------------------|

|            |           | 0                       |            | Qn                           | No change                                           |                  |

|            |           | 1                       |            | Qn                           | Toggle                                              |                  |

| <b>f</b> ) |           | modulus of<br>counter.  | a coun     | ter. Write the n             | umbers of flip flops required fo                    | r 2M             |

| Ans:       |           |                         | counter    | is defined as nur            | mber of states/clock the counter                    | Definition:      |

|            |           | countes.<br>The number  | s of flip  | flops required for           | or Mod-6 counter is 3.                              | No. of FF-<br>1M |

| <b>g</b> ) | State fu  | nction of p             | reset ar   | nd clear in flip f           | lop.                                                | 2M               |

|            | • ]       | Tence, the i            | uncum      | OT DECOUETR TO SE            | t a flip flop i.e. $O = I$ and the                  | table is         |

|            |           |                         |            | to clear a flip flo          | t a flip flop i.e. $Q = 1$ and the p i.e. $Q = 0$ . | optional)        |

|            | 1         | Function of o           | clear is t | to clear a flip flo          |                                                     |                  |

|            | CK        | Inputs  Cr              | clear is t | Output                       | p i.e. Q = 0.  Operation performed                  |                  |

|            | 1         | Function of o           | clear is t | Output $Q_{s+1}$ (Table 7.1) | Operation performed  Normal FLIP-FLOP               |                  |

|            | - СК<br>1 | Inputs  Cr              | clear is t | Output                       | p i.e. Q = 0.  Operation performed                  |                  |

### MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 – 2013 Certified)

|   | <b>b</b> ) | Convert –                                                                                | 4M    |

|---|------------|------------------------------------------------------------------------------------------|-------|

|   |            | $(255)_{10} = (?)_{16} = (?)_8$                                                          |       |

|   | Ange       | $(157)_{10} = (?)_{BCD} = (?)_{Excess3}$                                                 |       |

|   | Ans:       | (i) $(255)_{10} = (FF)_{16} = (377)_8$                                                   |       |

|   |            | $(255)_{10} = (FF)_{16}$                                                                 | 1 M   |

|   |            | 16   255 F (15) 1                                                                        |       |

|   |            | 16 255 F (15) T                                                                          |       |

|   |            |                                                                                          |       |

|   |            | $(255)_{10} = (377)_8$                                                                   |       |

|   |            | 8 255 7                                                                                  | 1 M   |

|   |            | 8 31 7                                                                                   | 1 1/1 |

|   |            | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                   |       |

|   |            |                                                                                          |       |

|   |            | (ii) $(157)_{10} = (000101010111)_{BCD} = (010010001010)_{Excess3}$                      |       |

|   |            |                                                                                          |       |

|   |            | $(157)_{10} = (000101010111)_{BCD}$                                                      |       |

|   |            | 1 5 7<br>0001 0101 0111                                                                  | 1 M   |

|   |            | 0001 0101 0111                                                                           |       |

|   |            | $(000101010111)_{BCD} = (010010001010) \text{ Excess3}$                                  |       |

|   |            | 11 111 111                                                                               | 1 M   |

|   |            | 0001 0101 0111                                                                           |       |

|   |            | + 0011 0011 0011<br>0100 1000 1010                                                       |       |

|   |            |                                                                                          |       |

|   | c)         | Draw the symbol, truth table and logic expression of any one universal                   | 4M    |

| - | <u> </u>   | logic gate. Write reason why it is called universal gate.                                |       |

|   | Ans:       | (Note: Any one universal gate has to be considered.) Universal Gates: NAND or NORSymbol: |       |

|   |            | Chiversal Gates. TVATAD of TVORSymbol.                                                   | 1 M   |

|   |            | <b>1</b> → 1 >-                                                                          |       |

|   |            | Truth table:                                                                             |       |

|   |            | ABYABY                                                                                   | 1 M   |

|   |            | 0 0 1 0 0 1                                                                              |       |

|   |            | 0 1 1 0 1 0                                                                              |       |

|   |            | 1 0 1 1 0 0                                                                              |       |

|   |            |                                                                                          |       |

|   |            | Logic expression:                                                                        | 435   |

|   |            | $Y = \overline{A \cdot B}$ $Y = (\overline{A + B})$                                      | 1 M   |

|   |            | NAND and NOR gates are called as "Universal Gate" as it is possible to                   |       |

|   |            | implement any Boolean expression using these gates.                                      | 1 M   |

|   |            |                                                                                          |       |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

| Q. 3 |            | <b>Attempt any THREE:</b>                                                                                  |                                    |                            | 12-Total    |  |

|------|------------|------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------|-------------|--|

|      | a)         | Compare TTL and CN (i) Propagation (ii) Power Dissi (iii) Fan-out (iv) Basic gate                          | •                                  | pasis of following:        | Marks<br>4M |  |

|      | Ans:       | <u>NOTE :- ( Rei</u>                                                                                       | levant points of comparison- 1     | M for each point)          | 1 Marks     |  |

|      |            | Parameter                                                                                                  | CMOS                               | TTL                        | each point  |  |

|      |            | Propagation delay                                                                                          | 70-105 nsec/more than TTL          | 10 nsec/Less than<br>CMOS  |             |  |

|      |            | Power Dissipation                                                                                          | Less 0.1 mW/Less than TTL          | More 10 mW/ More than CMOS |             |  |

|      |            | Fan-out                                                                                                    | 50/More than TTL                   | 10/Less than CMOS          |             |  |

|      |            | Basic gate                                                                                                 | NAND/NOR                           | NAND                       |             |  |

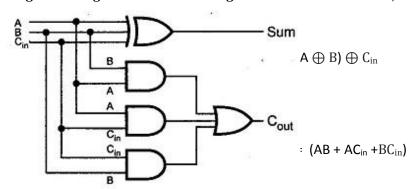

|      | <b>b</b> ) | Describe the function of full Adder Circuit using its truth table, K-Map simplification and logic diagram. |                                    |                            |             |  |

|      |            | Block diagram:  FULL ADDER                                                                                 | bits A and B, and carry C for Cour | rom the previous bit.      | 1M          |  |

|      |            |                                                                                                            |                                    |                            | 1M          |  |

(Autonomous) (ISO/IEC - 27001 – 2013 Certified)

### **Truth Table:**

|   | Input |     | Out | put   |

|---|-------|-----|-----|-------|

| Α | В     | Cin | Sum | Carry |

| 0 | 0     | 0   | 0   | 0     |

| 0 | 0     | 1   | 1   | 0     |

| 0 | 1     | 0   | 1   | 0     |

| 0 | 1     | 1   | 0   | 1     |

| 1 | 0     | 0   | 1   | 0     |

| 1 | 0     | 1   | 0   | 1     |

| 1 | 1     | 0   | 0   | 1     |

| 1 | 1     | 1   | 1   | 1     |

**1M**

**1M**

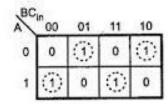

**K-Map :-**

For Carry (Cout)

For Sum

$C_{out} = AB+A C_{in}+B C_{in}$  Sum =  $\overline{A} \overline{B} C_{in}+\overline{A} \overline{B} \overline{C}_{in}+A\overline{B} \overline{C}_{in}+ABC_{in}$

### **Logic Diagram:**

(Note: Logic Diagram using basic or universal gate also can be consider)

| c)         | Realize the basic logic gates, NOT, OR and AND gates using NOR gates only.   | 4M    |  |  |  |  |

|------------|------------------------------------------------------------------------------|-------|--|--|--|--|

| Ans:       |                                                                              | 13.7  |  |  |  |  |

|            | ( NOT GATE USING NOR GATE:1 M )                                              | 1M    |  |  |  |  |

|            | AX                                                                           |       |  |  |  |  |

|            | where, $X = A$ NOR A $x = \overline{A}$                                      |       |  |  |  |  |

|            | (AND GATE USING NOR GATE:1.5 MARKS)                                          |       |  |  |  |  |

|            | A-1)                                                                         | 1.5M  |  |  |  |  |

|            | $\overline{Q} = \overline{A} + \overline{B} = \overline{A} + \overline{B}$   |       |  |  |  |  |

|            |                                                                              |       |  |  |  |  |

|            | =A.B $=$ A.B                                                                 |       |  |  |  |  |

|            | (OR GATE USING NOR GATE:1.5 MARKS)                                           |       |  |  |  |  |

|            |                                                                              |       |  |  |  |  |

|            |                                                                              | 1.5 M |  |  |  |  |

|            |                                                                              |       |  |  |  |  |

|            | $Q = \overline{\overline{A + B}}$                                            |       |  |  |  |  |

|            | =A+B                                                                         |       |  |  |  |  |

|            |                                                                              |       |  |  |  |  |

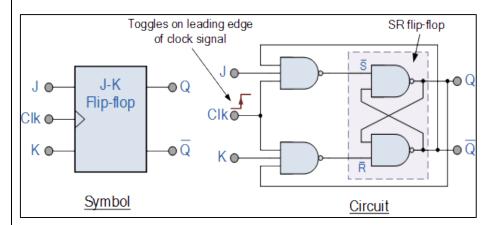

| <b>d</b> ) | Describe the working of JK flip-flop with its truth table and logic diagram. | 4M    |  |  |  |  |

| Ans:       | (Diagram-2 M, Working-1M, Truth table-1M)                                    |       |  |  |  |  |

|            | Truth Table :-                                                               | 1M    |  |  |  |  |

|            | Truth Table                                                                  |       |  |  |  |  |

|            | J K CLK Q                                                                    |       |  |  |  |  |

|            | 0 0 † Q <sub>0</sub> (no change)<br>1 0 † 1                                  |       |  |  |  |  |

|            |                                                                              |       |  |  |  |  |

|            | $1  1  \uparrow  \overline{Q}_0 \text{ (toggles)}$                           |       |  |  |  |  |

|            |                                                                              |       |  |  |  |  |

|            |                                                                              |       |  |  |  |  |

$\begin{array}{c} (Autonomous) \\ (ISO/IEC - 27001 - 2013 \; Certified) \end{array} \\$

### Diagram:-

2M

#### **Working:**-

The **JK flip flop** is basically a gated SR flip-flop with the addition of a clock input circuitry that prevents the illegal or invalid output condition that can occur when both inputs S and R are equal to logic level "1". Due to this additional clocked input, a JK flip-flop has four possible input combinations, "logic 1", "logic 0", "no change" and "toggle".

**1M**

Both the S and the R inputs of the previous SR bistable have now been replaced by two inputs called the J and K inputs, respectively after its inventor Jack Kilby. Then this equates to: J = S and K = R.

The two 2-input AND gates of the gated SR bistable have now been replaced by two 3-input NAND gates with the third input of each gate connected to the outputs at Q and Q. This cross coupling of the SR flip-flop allows the previously invalid condition of S = "1" and R = "1" state to be used to produce a "toggle action" as the two inputs are now interlocked.

If the circuit is now "SET" the J input is inhibited by the "0" status of Q through the lower NAND gate. If the circuit is "RESET" the K input is inhibited by the "0" status of Q through the upper NAND gate. As Q and Q are always different we can use them to control the input. When both inputs J and K are equal to logic "1", the JK flip flop toggles

| Q. 4 | <b>A</b> ) | Attempt any THREE of the following:                                                                                                                                                | 12-Total    |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|      | a)         | Draw and explain working of 4 bit serial Input parallel Output shift                                                                                                               | Marks<br>4M |

|      | Ange       | register. (Diagram:2M,Explaination:2M)                                                                                                                                             |             |

|      | Ans:       | (Diagram: 2Wi,Explamation: 2Wi)                                                                                                                                                    |             |

|      |            | Diagram :-                                                                                                                                                                         | 21/4        |

|      |            | 4-bit Parallel Data Output                                                                                                                                                         | 2M          |

|      |            | $Q_A$ $Q_B$ $Q_C$ $Q_D$                                                                                                                                                            |             |

|      |            |                                                                                                                                                                                    |             |

|      |            | Serial D Q D Q D Q                                                                                                                                                                 |             |

|      |            | Data in FFA FFB FFC FFD                                                                                                                                                            |             |

|      |            | CLK CLR CLR CLR                                                                                                                                                                    |             |

|      |            | Clear                                                                                                                                                                              |             |

|      |            | Clock                                                                                                                                                                              |             |

|      |            |                                                                                                                                                                                    |             |

|      |            | Explaination :-                                                                                                                                                                    |             |

|      |            | If a logic "1" is connected to the DATA input pin of FFA then on the first                                                                                                         |             |

|      |            | clock pulse the output of FFA and therefore the resulting Q <sub>A</sub> will be set HIGH                                                                                          | 2M          |

|      |            | to logic "1" with all the other outputs still remaining LOW at logic "0".  Assume now that the DATA input pin of FFA has returned LOW again to logic                               | 2141        |

|      |            | "0" giving us one data pulse or 0-1-0.                                                                                                                                             |             |

|      |            | The second clock pulse will change the output of FFA to logic "0" and the                                                                                                          |             |

|      |            | output of FFBand Q <sub>B</sub> HIGH to logic "1" as its input D has the logic "1" level on it from Q <sub>A</sub> . The logic "1" has now moved or been "shifted" one place along |             |

|      |            | the register to the right as it is now at QA.                                                                                                                                      |             |

|      |            | When the third clock pulse arrives this logic "1" value moves to the output                                                                                                        |             |

|      |            | of FFC ( $Q_C$ ) and so on until the arrival of the fifth clock pulse which sets all the outputs $Q_A$ to $Q_D$ back again to logic level "0" because the input                    |             |

|      |            | to FFA has remained constant at logic level "0".                                                                                                                                   |             |

|      |            | The effect of each clock pulse is to shift the data contents of each stage one                                                                                                     |             |

|      |            | place to the right, and this is shown in the following table until the complete data value of 0-0-0-1 is stored in the register. This data value can now be read                   |             |

|      |            | directly from the outputs of Q <sub>A</sub> to Q <sub>D</sub> .                                                                                                                    |             |

|      |            | Then the data has been converted from a serial data input signal to a parallel                                                                                                     |             |

|      |            | data output. The truth table and following waveforms show the propagation of the logic "1" through the register from left to right as follows.                                     |             |

|      |            | 5                                                                                                                                                                                  |             |

|      |            | Basic Data Movement Through A Shift Register                                                                                                                                       |             |

|      |            | Basic Data Movement Through A Shift Register                                                                                                                                       |             |

|            |             | Clock Pulse No                                           | QA   | QB | QC                  | QD |               |           |

|------------|-------------|----------------------------------------------------------|------|----|---------------------|----|---------------|-----------|

|            |             | 0                                                        | 0    | 0  | 0                   | 0  |               |           |

|            |             | 1                                                        | 1    | 0  | 0                   | 0  |               |           |

|            |             | 2                                                        | 0    | 1  | 0                   | 0  |               |           |

|            |             | 3                                                        | 0    | 0  | 1                   | 0  |               |           |

|            |             | 4                                                        | 0    | 0  | 0                   | 1  |               |           |

|            |             | 5                                                        | 0    | 0  | 0                   | 0  |               |           |

|            |             |                                                          |      |    |                     |    |               |           |

| <b>b</b> ) | Draw 16:1 M | UX tree using 4:1                                        | MUX. |    |                     |    |               | 4M        |

|            |             |                                                          |      |    |                     |    |               | <b>4M</b> |

|            | 12          | 4X1<br>MUX<br>S1 S0<br>4X1<br>MUX<br>4X1<br>MUX<br>S1 S0 |      |    | 4X1<br>MUX<br>S3 S2 |    | Output<br>(f) | 4.V1      |

| c)   | Calculate analog output of 4 bit DAC for digital input 1101. Assume $V_{FS} = 5V$ .                      | 4M |  |  |

|------|----------------------------------------------------------------------------------------------------------|----|--|--|

| Ans: | (Formula- 1M, Correct problem solving- 3M)                                                               |    |  |  |

|      | Formula :-                                                                                               | 1M |  |  |

|      | $\mathbf{V_R} = \mathbf{V_{FS}}$                                                                         |    |  |  |

|      | $V_o = V_R [d_1 2^{-1} + d_2 2^{-2} + + d_n 2^{-n}]$                                                     | 3M |  |  |

|      | $= 5(1x2^{-1} + 1x2^{-2} + 0x2^{-3} + 1x2^{-4})$ $= 5(0.5 + 0.25 + 0 + 0.0625)$ $= 4.0625 \text{ Volts}$ |    |  |  |

|      | OR                                                                                                       |    |  |  |

|      | $V_{FS} = V_R \cdot \left( \frac{b3}{2} + \frac{b2}{4} + \frac{b1}{8} + \frac{b0}{16} \right)$           |    |  |  |

|      | Note – (Since $V_R$ is not given find $V_R$ )                                                            |    |  |  |

|      | Full Scale o/p mean                                                                                      |    |  |  |

|      | b3 b2 b1 b0 = 1111                                                                                       |    |  |  |

|      | $V_{FS} = 5V$                                                                                            |    |  |  |

|      | $5 = V_R \cdot \left(\frac{1}{2} + \frac{1}{4} + \frac{1}{8} + \frac{1}{16}\right)$                      |    |  |  |

|      | $V_R = 5.33$                                                                                             |    |  |  |

|      | For digital i/p b3 b2 b1 b0 = 1101                                                                       |    |  |  |

|      | $V_0 = 5.33 \left( \frac{1}{2} + \frac{1}{4} + \frac{0}{8} + \frac{1}{16} \right)$                       |    |  |  |

|      | $\mathbf{V}_0 = \mathbf{4.33V}$                                                                          |    |  |  |

| d)   | State De Morgan's theorem and prove any one.                                                             | 4M |  |  |

| Ans: | (Each State and proof using table- 2M each)                                                              |    |  |  |

|      |                                                                                                          | 2M |  |  |

|      |                                                                                                          |    |  |  |

|      |                                                                                                          |    |  |  |

|      |                                                                                                          |    |  |  |

$\begin{array}{c} (Autonomous) \\ (ISO/IEC - 27001 - 2013 \; Certified) \end{array} \\$

i)  $\overline{AB} = \overline{A} + \overline{B}$

It states that compliment of product is equal to sum of their compliments.

| 1 | 2 | 3               | 4              | 5              | 6                             |

|---|---|-----------------|----------------|----------------|-------------------------------|

| A | В | $\overline{AB}$ | $\overline{A}$ | $\overline{B}$ | $\overline{A} + \overline{B}$ |

| 0 | 0 | 1               | 1              | 1              | 1                             |

| 0 | 1 | 1               | 1              | 0              | 1                             |

| 1 | 0 | 1               | 0              | 1              | 1                             |

| 1 | 1 | 0               | 0              | 0              | 0                             |

Column 03 = column 06

i.e.  $\overline{AB} = \overline{A} + \overline{B}$

Hence proved

OR

ii)  $\overline{A+B} = \overline{A} \cdot \overline{B}$

It states that complement of sum is equal to product of their complements.

|   |   |                  | 1 1            |                |                                   |

|---|---|------------------|----------------|----------------|-----------------------------------|

| 1 | 2 | 3                | 4              | 5              | 6                                 |

| A | В | $\overline{A+B}$ | $\overline{A}$ | $\overline{B}$ | $\overline{A} \cdot \overline{B}$ |

| 0 | 0 | 1                | 1              | 1              | 1                                 |

| 0 | 1 | 0                | 1              | 0              | 0                                 |

| 1 | 0 | 0                | 0              | 1              | 0                                 |

| 1 | 1 | 0                | 0              | 0              | 0                                 |

Column 03 = column 06

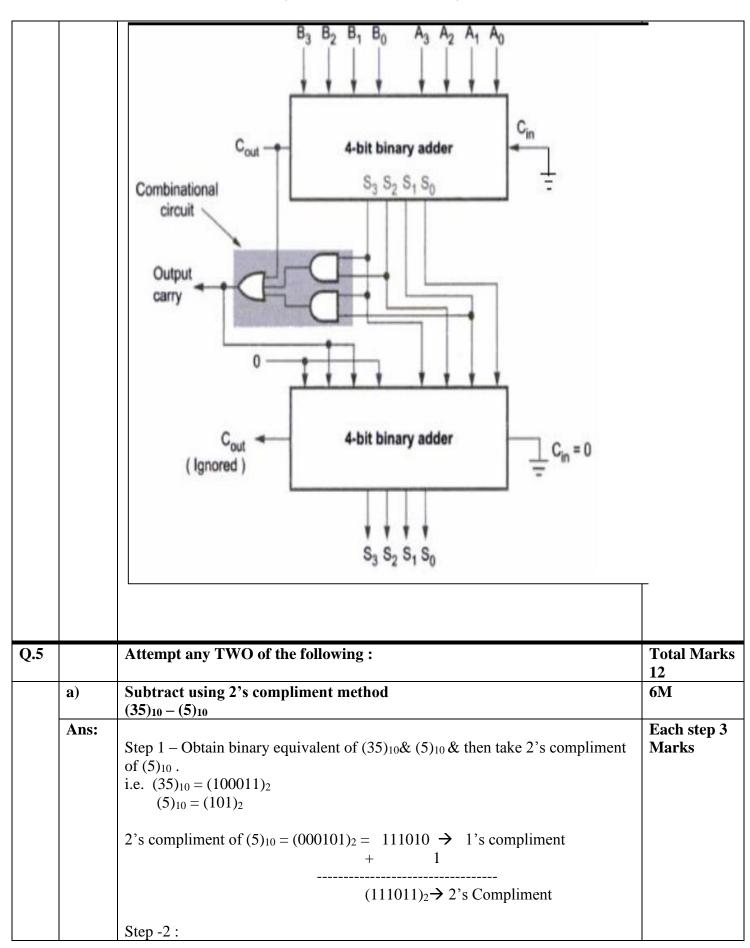

Design one digit BCD Adder using IC 7483

$\therefore \overline{A+B} = \overline{A} \cdot \overline{B}$

Hence proved.

| Ans: | (Diagram:4M)                                                                 |    |

|------|------------------------------------------------------------------------------|----|

|      | (Note: Labeled combinational circuit can be drawn using universal gate also) | 4M |

**2M**

### MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 – 2013 Certified)

|            |                    | 1          | 01111    | 11<br>0 |         |         | 1       |         |                | •,•            | C              | .1             |           |       |

|------------|--------------------|------------|----------|---------|---------|---------|---------|---------|----------------|----------------|----------------|----------------|-----------|-------|

|            | discard<br>Therefo |            | rry ger  | nerate  | ed      |         |         |         | is in p        | OSITIVE        | ; iorm         | ı, so will     |           |       |

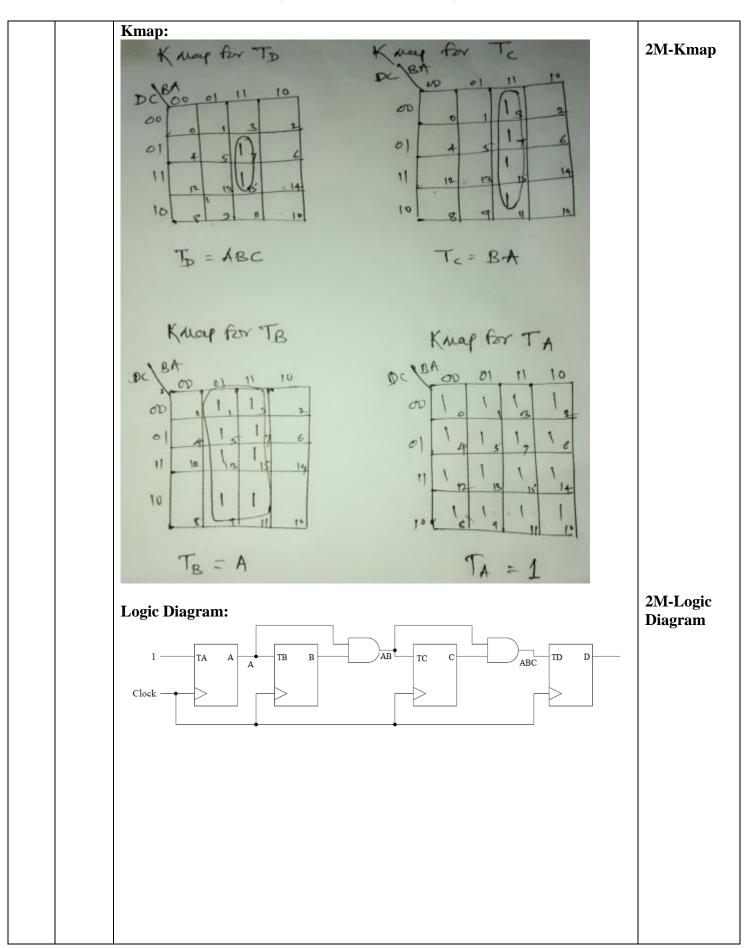

| <b>b</b> ) | Design             | a 4 bi     | t syncl  | hron    | ous co  | unter   | and d   | lraw i  | ts logi        | c diag         | ram.           |                | 6M        |       |

| Ans:       | State T            | able:      |          |         |         |         |         |         |                |                |                |                |           |       |

|            |                    |            | ent stat |         | D+      |         | state   | A ÷     |                | lip flo        |                |                |           |       |

|            |                    | D C        |          | A 0     | D+<br>0 | C+<br>0 | B+<br>0 | A+<br>1 | T <sub>D</sub> | T <sub>C</sub> | T <sub>B</sub> | T <sub>A</sub> |           |       |

|            |                    | 0 0        |          | 1       | 0       | 0       | 1       | 0       | 0              | 0              | 1              | 1              |           |       |

|            |                    | 0 0        |          | 0       | 0       | 0       | 1       | 1       | 0              | 0              | 0              | 1              | 2M<br>tab | -Stat |

|            |                    | 0 0        | 1        | 1       | 0       | 1       | 0       | 0       | 0              | 1              | 1              | 1              |           | 10    |

|            | (                  | 0 1        | 0        | 0       | 0       | 1       | 0       | 1       | 0              | 0              | 0              | 1              |           |       |

|            | (                  | 0 1        | 0        | 1       | 0       | 1       | 1       | 0       | 0              | 0              | 1              | 1              |           |       |

|            |                    | 0 1        | 1        | 0       | 0       | 1       | 1       | 1       | 0              | 0              | 0              | 1              |           |       |

|            |                    | 0 1        |          | 1       | 1       | 0       | 0       | 0       | 1              | 1              | 1              | 1              |           |       |

|            |                    | 1 0        |          | 0       | 1       | 0       | 0       | 1       | 0              | 0              | 0              | 1              |           |       |

|            |                    | 1 0        |          | 1       | 1       | 0       | 1       | 0       | 0              | 0              | 1              | 1              |           |       |

|            |                    | 1 0        |          | 0       | 1       | 0       | 1       | 1       | 0              | 0              | 0              | 1              |           |       |

|            |                    | 1 0<br>1 1 |          | 0       | 1       | 1       | 0       | 0       | 0              | 0              | 1 0            | 1              |           |       |

|            |                    | 1 1        |          | 1       | 1       | 1       | 1       | 0       | 0              | 0              | 1              | 1              |           |       |

|            |                    | 1 1        |          | 0       | 1       | 1       | 1       | 1       | 0              | 0              | 0              | 1              |           |       |

|            |                    | 1 1        |          | 1       | 0       | 0       | 0       | 0       | 1              | 1              | 1              | 1              |           |       |

|            |                    |            |          |         |         |         |         |         |                |                |                |                |           |       |

### MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(Autonomous) (ISO/IEC - 27001 – 2013 Certified)

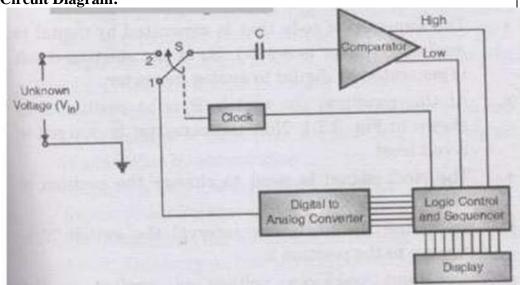

| c)   | Describe the working of Successive Approximation ADC. Define                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6M                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Anc. | Resolution and conversion time associate with ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |

| Ans: | Circuit Diagram:  Voltage comparator  Voltage Control circuit  NSB  LSB  Successive Approximation Register  Output buffer register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2 Marks<br>Diagram     |

|      | When the start signal goes low the successive approximation register SAR is cleared and output voltage of DAC will be 0V. When start goes high the conversion starts.  After starts, during first clock pulse the control circuit set MSB bit so SAR output will be 1000 0000. This is connected as input to DAC so output of                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 Marks<br>Explanation |

|      | DAC is (analog output) compared with $V_{in}$ input voltage. If $V_{DAC}$ is more than $V_{in}$ the comparator output $-V_{sat}$ , if $V_{DAC}$ is less than $V_{in}$ , the comparator output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |

|      | If output of DAC i.e. $V_{DAC}$ is $+V_{sat}$ (i.e unknown analog input voltage $V_{in} > V_{DAC}$ ) then MSB bit is kept set, otherwise it is reset. Consider MSB is set so SAR will contain 1000 0000. The next clock pulse will set next bit i.e $D_6$ a digital output of 1100 0000. The output voltage of DAC i.e $V_{DAC}$ is compared with $V_{in}$ , if it is $+V_{sat}$ the $D_6$ bit is kept as it is, but if it is $-V_{sat}$ the $D_6$ bit reset. The process of checking and taking decision to keep bit set or to reset is continued upto $D_0$ . Then the DAC input will be digital data equal to analog input. When the conversation if finished the control circuits sends out an end of conversion signal and data is locked in buffer register | 1 Marks<br>Each        |

(ISO/IEC - 27001 - 2013 Certified)

Resolution: The voltage input change necessary for a one bit change in the output is called resolution.

Conversion Time: The conversion time is the time required for conversion from an analog input voltage to the stable digital output

#### OR

#### **Circuit Diagram:**

2 Marks Diagram

#### **Explanation:**

DAC= Digital to Analog converter

EOC= End of conversion

SAR =Succesive approximation register

S/H= Sample and hold circuit

Vin= input voltage

Vref= reference voltage

The successive approximation Analog to Digital converter circuit typically consisting of four sub circuits-

- 1. A sample and hold circuit to acquire the input voltage Vin.

- 2. An analog voltage comparator that compares Vin to the output of internal DAC and outputs the result of comparison to successive approximation register(SAR).

- 3. SAR sub circuits designed to supply an approximate digital code of Vin to the internal DAC.

- 4. An internal reference DAC that supplies the comparator with an analog voltage equivalent of digital code output of SAR for comparison with Vin.

The successive approximation register is initialized so that most significant bit (MSB) is equal to digital 1. This code is fed into DAC which the supplies the analog equivalent of this digital code Vref/2 into the comparator circuit for the comparison with sampled input voltage. If this analog voltage exceeds Vin the comparator causes the SAR to reset the bit, otherwise a bit is left as 1. Then the

2 Marks Explanation

(Autonomous) (ISO/IEC - 27001 – 2013 Certified)

next bit is set to 1 and the same test is done continuing this binary search until every bit in the SAR has been tested. The resulting code is the digital approximation of the sampled input voltage and is finally output by DAC at end of the conversion (EOC).

Resolution and conversion time associate with ADC-

#### **Resolution**:

It is the maximum number of digital output codes.

Resolution= 2^n

(OR)

It is defined as the ratio of change in the value of input analog voltage required to change the digital output by 1 LSB.

$$\therefore \text{ Resolution } = \frac{V_{FS}}{2^n - 1}$$

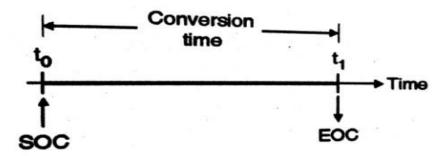

#### **Conversion time:**

The time difference between two instants i.e. 'to' where SOC signal is given as input to the ADC and 't1' where EOC signal we get as output from ADC. it should be small as possible.

1 Marks each

| Q.6 |      | Attempt an                                                                   |                |                       |                |        |                |                | Total Marks<br>12       |

|-----|------|------------------------------------------------------------------------------|----------------|-----------------------|----------------|--------|----------------|----------------|-------------------------|

|     | a)   | Design 4 bit                                                                 | t Binary to    | Gray code             | conv           | erter. |                |                | 6M                      |

|     | Ans: | Truth Table                                                                  |                |                       | y code         |        |                |                | 2M for truth table      |

|     |      |                                                                              | Binary Inpi    |                       |                |        | y output       |                | 1/2 6                   |

|     |      | B3 B2                                                                        | B <sub>1</sub> | <b>B</b> <sub>0</sub> | G <sub>3</sub> |        | G <sub>1</sub> | G <sub>0</sub> | 1/2m for                |

|     |      | $\begin{array}{ c c c } \hline 0 & 0 \\ \hline 0 & 0 \\ \hline \end{array}$  | 0              | 0                     | 0              | 0      | 0              | 0              | each output<br>equation |

|     |      | $\begin{array}{ c c c } \hline 0 & 0 \\ \hline 0 & 0 \\ \hline \end{array}$  | 0              | 0                     | 0              | 0      | 0              | 1              | 2M for                  |

|     |      | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                       | 1 1            | 1                     | 0              | 0      | 1 1            | 0              | realization             |

|     |      | $\begin{vmatrix} 0 & 0 \\ 0 & 1 \end{vmatrix}$                               | 0              | 0                     | 0              | 1      | 1              | 0              | using gates             |

|     |      | $\begin{vmatrix} 0 & 1 \\ 0 & 1 \end{vmatrix}$                               | 0              | 1                     | 0              | 1      | 1              | 1              | using gates             |

|     |      | $\begin{vmatrix} 0 & 1 \\ 0 & 1 \end{vmatrix}$                               | 1              | 0                     | 0              | 1      | 0              | 1              |                         |

|     |      | $\begin{vmatrix} 0 & 1 \\ 0 & 1 \end{vmatrix}$                               | 1              | 1                     | 0              | 1      | 0              | 0              |                         |

|     |      | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                       | 0              | 0                     | 1              | 1      | 0              | 0              |                         |

|     |      | $\begin{array}{ c c c c }\hline 1 & 0 \\\hline 1 & 0 \\\hline \end{array}$   | 0              | 1                     | 1              | 1      | 0              | 1              |                         |

|     |      | $\begin{array}{ c c c c }\hline 1 & 0 \\\hline 1 & 0 \\\hline \end{array}$   | 1              | 0                     | 1              | 1      | 1              | 1              |                         |

|     |      | $\begin{array}{ c c c c c }\hline 1 & 0 \\\hline 1 & 0 \\\hline \end{array}$ | 1              | 1                     | 1              | 1      | 1              | 0              |                         |

|     |      | $\begin{array}{ c c c c c }\hline 1 & 0 \\\hline 1 & 1 \\\hline \end{array}$ | 0              | 0                     | 1              | 0      | 1              | 0              |                         |

|     |      | $\begin{array}{ c c c c c }\hline 1 & 1 \\\hline 1 & 1 \\\hline \end{array}$ | 0              | 1                     | 1              | 0      | 1              | 1              |                         |

|     |      | $\begin{array}{ c c c c c }\hline 1 & 1 \\\hline \end{array}$                | 1              | 0                     | 1              | 0      | 0              | 1              |                         |

|     |      | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                       | 1              | 1                     | 1              | 0      | 0              | 0              |                         |

|     |      | K-MAP FO                                                                     |                | 01                    |                | 11     | 10             |                |                         |

|     |      | 63B2 00                                                                      | 0              | 0                     |                | 0      | 0              |                |                         |

|     |      | 01                                                                           | 0              | 0                     |                | 0      | 0              |                |                         |

|     |      | 11                                                                           | 1              | 1                     |                | 1      | 1              |                |                         |

|     |      | 10                                                                           | 1              | 1                     |                | 1      | 1              |                |                         |

|     |      | G3=B3                                                                        |                |                       |                | •      | •              |                |                         |

| <b>B</b> 31  | `\         | <sup>)</sup> oo | 01 | 11      | 10      |  |

|--------------|------------|-----------------|----|---------|---------|--|

|              | 00         | 0               | 0  | 0       | 0       |  |

|              | 01         | 1               | 1  | 1       | 1       |  |

|              | 11         | 0               | 0  | 0       | 0       |  |

|              | 10         | 1               | 1  | 1       | 1       |  |

| G2=1<br>= B3 | XOR I      | - B2 B3<br>32   |    |         |         |  |

|              | AP FOI     |                 |    |         |         |  |

|              | 1          | 80 00           | 01 | 11<br>I | 10<br>I |  |

| 83           | B2 \<br>00 | 0               | 0  | 1       | 1       |  |

|              | 01         | 1               | 1  | 0       | 0       |  |

|              | 11         | 1               | 1  | 0       | 0       |  |

|              | 10         | 0               | 0  | 1       | 1       |  |

| G1=B2 B1 +              | B2 B1            |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|-------------------------|------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| = B1 XOR B              | 32               |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| K-MAP FOI               | R G0:            |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B1E<br>B3B2             | 80 <sub>00</sub> | 01             | 11             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 00                      | 0                | 1              | 0              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 01                      | 0                | 1              | 0              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 11                      | 0                | 1              | 0              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 10                      | 0                | 1              | 0              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| G0=B1B0 -<br>= B1 XOR I |                  |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |