(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

### **SUMMER - 16 EXAMINATION**

Subject Code:17664 <u>Model Answer</u>

**Important Instructions to examiners:**

- 1) The answers should be examined by keywords and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to asses understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance. (Not applicable subject English and Communication Skills.)

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figure drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

\_\_\_\_\_\_

| Q. No. | Question & Answer                                                                                                                                                                                                                                                                                                                                                                                | Remark                       | Total<br>Marks |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|

| Q1 A   | Attempt any THREE                                                                                                                                                                                                                                                                                                                                                                                |                              | 12             |

| (a)    | Define automation. State need of automation                                                                                                                                                                                                                                                                                                                                                      |                              | 04             |

| Ans.   | Definition: The technology which can perform all processes or system to operate automatically (without manual operator) is called Automation.  OR  The technique consist of mechanical, electrical, control system with base applications from physics to operate process or system without manual operator is called as Automation.  OR  Any other relevant definition shall be considered      | 01 mark<br>for<br>Definition |                |

|        | <ul> <li>Need of Automation in process: (Any THREE points)</li> <li>To fulfill the demand of product at right time.</li> <li>To reduce the human errors and involvement of human being in the process.</li> <li>For better productivity.</li> <li>For better control of process.</li> <li>For better quality.</li> <li>For reducing man power.</li> <li>For reducing cost of product.</li> </ul> | 01 mark<br>for each<br>point |                |

|        | Note: Any other relevant points should be considered                                                                                                                                                                                                                                                                                                                                             |                              |                |

| (b)    | Draw block diagram of AC input module of PLC and write function of threshold detector block.                                                                                                                                                                                                                                                                                                     |                              | 04             |

|        | tunction of threshold detector block.                                                                                                                                                                                                                                                                                                                                                            |                              |                |

**SUMMER - 16 EXAMINATION** Subject Code:17664 **Model Answer**

| <b>†</b> | Bridge Rectifier Signal Rectifier Filter Status table  Noise and debounce filter Logic CPU status table  LED | 02 mark<br>for<br>diagram |     |

|----------|--------------------------------------------------------------------------------------------------------------|---------------------------|-----|

| Fu       | nction of Threshold detector block:                                                                          |                           |     |

| •        | Threshold detection circuitry detects whether the incoming                                                   |                           |     |

|          | signal has reached or exceeded a predetermined voltage level                                                 |                           |     |

|          | for a predetermined time and whether it should be classified as                                              | 02 mark                   |     |

|          | a valid ON or OFF signal.<br>A typical valid OFF state is below 0 and 20 or 30 $V_{AC}$                      | for function              |     |

|          | depending on the module's manufacture and a valid ON state is                                                |                           |     |

|          | between 80 and 132 $V_{AC}$ again depending on the module's                                                  |                           |     |

|          | manufacturer.                                                                                                |                           |     |

| •        | The signal area between the upper voltage limit for a valid OFF                                              |                           |     |

|          | state (20 $V_{AC}$ ) and minimum voltage for a valid ON state (80                                            |                           |     |

|          | V <sub>AC</sub> ) is called undefined zone or input state not guaranteed                                     |                           |     |

|          | <b>zone</b> . The signals falling within this undefined zone may be ON                                       |                           |     |

|          | or OFF making them unstable and unreliable.                                                                  |                           |     |

| •        | Filtering and time delays are used to filter out electrical noise                                            |                           |     |

|          | that may be interrupted as a false input pulse.                                                              |                           |     |

| •        | To eliminate the possibility a faulty operation due to electrical                                            |                           |     |

|          | noise, a valid AC input signal must not only be a specific                                                   |                           |     |

|          | value, but must be present for a specific amount of time before                                              |                           |     |

|          | the input module allows the valid signal to pass to the isolation                                            |                           |     |

|          | section.                                                                                                     |                           | 0.4 |

|          | scribe functioning of NO, NC, Latch and Unlatch instructions h their symbols.                                |                           | 04  |

| _        | 1) NO (Examine if Closed)                                                                                    |                           |     |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **SUMMER - 16 EXAMINATION**

Subject Code:17664

**Model Answer**

I:010

01 mark

- Examines a bit for an On condition

- Use the XIC instruction in your ladder logic to determine if a bit is ON.

- 0 = False

- 1 = True

- 2) NC (Examine if Open)

I:0/1

01 mark

- Examines a bit for an off condition.

- Use an XIO instruction in your ladder logic to determine if a bit if off.

- 1 = True

- 0 = False

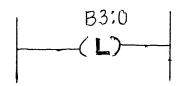

- 3) OUTPUT LATCH

01 mark

- Turns a bit on when the rung is executed, and this bit retains its state when the rung is not executed or a power cycle power occurs.

- 4) OUTPUT UNLATCH

01 mark

• Turns a bit off when the rung is executed, and this bit retains its state when the rung is not executed or when power cycle occurs.

### **SUMMER - 16 EXAMINATION**

Subject Code:17664

| <b>d</b> )  | Draw labeled block diagram of analog output module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         | 04 |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|--|--|

| Ans         | Block diagram of analog output module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 04 Marks<br>for labeled<br>diagram      |    |  |  |

|             | O/P data table CPU Logic orrcuit Optical isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | diagram                                 |    |  |  |

|             | Analog O/P device  Analog O/P voltage  D/A converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |    |  |  |

| <b>B</b> )  | Attempt any ONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         | 06 |  |  |

| 1)          | i)Enlist advantages of PLC over relay logic ii)Enlist any four output devices used with PLC. And state their uses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | 06 |  |  |

| Ans         | i) Advantages of PLC over relay logic: (Any three)  1. PLC are more flexible than relay logic circuit  2. PLC offer easy troubleshooting and correcting any errors.  3. PLC are designed for high speed and real time applications.  4. Power required for PLC is less than relay control logic.  5. PLC is more reliable than relay and life is more than relay.  6. PLC system has less downtime than relay logic.  7. Internal memory available in PLC system and not in relay logic.  8. PLC system are quickly reprogrammable over relay logic.  9. Maintenance cost of PLC is less than relay logic. |                                         |    |  |  |

|             | ii)Output devices used with PLC: (Any two)  1.Motor  2.Solenoid  3.Output relay  4.Timers  5.Heating devices  6.Alarms  7.Indicator Lamps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01 Mark<br>for each<br>Output<br>device |    |  |  |

|             | Uses of Output devices: (Any one)  1. These are used to produce actual work output.  2. Output relay are used in control system.  3. Relay is used as power switch.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 01 Mark                                 |    |  |  |

| <b>)</b>    | Draw neat block diagram of analog input module and explain,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 06 |  |  |

|             | enlist its two specifications  Diagram of analog input module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 02 Mark                                 |    |  |  |

| <b>A</b> ns | Diagram of analog input module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 02 IVIAIK                               |    |  |  |

### **SUMMER - 16 EXAMINATION**

Subject Code:17664

| Ans | i)PLC programming languages:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----|

| a)  | i)Give detailed classification of PLC programming languages ii)Explain sequencer instruction with example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | 08 |

| 2)  | Attempt any TWO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   | 16 |

|     | OR Any other relevant specification shall be considered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |    |

|     | <ul> <li>ADC with 14 bits</li> <li>ADC with LSB resolution for voltage i/p 305 microvolt</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |    |

|     | <ul> <li>Module with 2,4, 8 selectable of voltage or current</li> <li>Module with 16 single ended for voltage or current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | for each<br>Specificati<br>on     |    |

|     | <ul> <li>i/p accepted signal levels are 0 to 10V dc, -10V to +10 V dc, 4 to 20 mA</li> <li>Module with 2 ,4, 8 differential of voltage or current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01 Mark                           |    |

|     | Specification of analog input module: (Any two)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |    |

|     | Explanation:-  Analog input module interface a PLC to analog input signals. It gives ability to PLC to monitor a continuously changing input signals such as pressure, temperature, flow etc. The module converts analog input signals to 16 bit binary values storage in the processor's input status table. Analog modules are designed to accept current and voltage signals such as 0-10 Vdc,-10-10 Vdc,0-5Vdc and 0-20mA,4-20mA,-20 -20mA etc. When signal reaches an input module,it is rich in different noise signals. The signal is freed from noise through noise minimization circuits. The signal is then digitized and sent to logic section through an isolation circuit. The logic section allows the digitized signal to go to the CPU following the predetermined logic. | 02 Mark<br>for<br>explanatio<br>n |    |

|     | Analog AC Voltage Input  Noise Minimisation  A/D Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | for<br>diagram                    |    |

Subject Code: 17664

### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **SUMMER - 16 EXAMINATION**

**Model Answer**

\_\_\_\_\_

- This standard specifies five languages divided into two parts namelygraphical languages and text-based languages.

- A) Graphical languages:

- i) Ladder Logic Diagram (LD)

- ii) Function Block Diagram (FBD)

- iii) Sequential Function Chart or Grafcet (SFC)

- B) Text-based languages:

- i) Instruction List (IL)

- ii) Structured Text (ST)

## ii)Description of Sequencer instruction with example.

PLC sequencer replaces the mechanical drum sequence that was used to control the sequences of repeatable operations. It acts as pointer and points one of the word from block of data words stored in memory. It fetches the words one at a time from memory and transfer or move to another memory or to the output. When block of data is finished the PLC sequencer again point the first word from the block and process begins again.

Traffic light controller is a simple example of sequencer which is controlled with electronics and PLC sequencer output.16 lights are used for output.each light represent one bit address of output word 050.the lights are programmed in a four step sequence to simulate the operation of two way traffic light .Data are entered into word file for each sequencer step as shown fig.

15 14 13 12 11 10 Output Word 050 0 0 0 0 0 0 address Step 1 0 0 0 0 Word 060 0 0 0 0 0 0 Step 2 0 0 0 0 0 0 0 0 Word 061 Four-word file located in Step 3 0 0 0 0 0 0 0 1 0 0 0 0 0 Word 062 memory Step 4 0 0 0 0 0 Word 063 0 0 0

04 Marks for classificati on

04 Marks For descriptio

Subject Code: 17664

### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

## (ISO/IEC - 27001 - 2005 Certified)

#### **SUMMER - 16 EXAMINATION**

<u>Model Answer</u>

When sequencer is activated and advanced to step 1 the binary information in word 060 of file is transferred into word 050 of output as a result light 1 and 12 are switched ON and rest remains off. Advancing the sequencer to step 2 will transfer the data from 061 to word 050, as are sult lamp 1 and 8 will be on and all the rest will be off and thus advancement in step 3 and step 4 is followed and finally when last step is reached, the sequencer is either automatically or manually reset to step 1. OR Any other sequencer instruction SQI/SQL/SQO with example should be considered 08 b) A railway station has 3 platforms A,B and C. One train is coming into station. The entry to this train is given to platform A if platform A is empty, if both platforms A and B are occupied then it has to be given entry to platform C, if all platforms are full then train has to wait. Design necessary ladder diagram with proper assumption and truth table. Ans The input signals with address are as follows, 02 marks Ta- Train present at A => I:0/1Proper I/O Tb - Train present at B = 1:0/2Assumptio Tc - Train present at  $C \Rightarrow I:0/3$ ns(address ing) The outputs with address are as, Pa - Go to platform A => 0:0/1Pb- Go to platform  $B \Rightarrow O:0/2$ Pc - Go to platform  $C \Rightarrow O:0/3$ W - wait => 0.0/402 marks Input Input Output Output Output Output Input for truth Ta Tb Tc Pa Pb Pc W table 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 0 0 0 1 0 1 0 1 1 1 0 0 1

**SUMMER - 16 EXAMINATION** Subject Code:17664

|     | Y 11 1                                                                                                                                                                                                                                                                                                                       | <u> </u>                             |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----|

|     | I:0/1                                                                                                                                                                                                                                                                                                                        | 04 marks<br>for<br>ladder<br>diagram |    |

| c)  | Design a traffic light control program with following conditions:  (1) Two inputs – START & STOP (Both push buttons)  (2) Three outputs –Red ,Green and Yellow lamps  (3) Repeat cycle given in fig.1 until, stop button is pressed.  Remain ON for 15 Sec. then OFF  Yellow  Remain ON for 25 Sec. then OFF  O Start O Stop |                                      | 08 |

| Ans | No of Inputs Start - I:0/0 Stop - I:0/1 No of Outputs  RED Lamp - O:0/0 GREEN Lamp - O:0/1 YELLOW Lamp - O:0/2                                                                                                                                                                                                               | 02 Marks<br>for I/O<br>addressing    |    |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### **SUMMER - 16 EXAMINATION**

Subject Code:17664

### **Model Answer**

I:0/2 I:0/I TIMER ON DELAY 06 marks Times T4:0 Time base 1.0s. Preset 15se Acumulator 0 for ladder diagram T4:0/TT TIMER ON DELAY Times T4:1 T4:0/DN Time base 1.0 Preset 25 sec Accumulator 0 T4:1/TT C >0:012 GREEN T4:1/DN TIMER ON DELAY Timer T4:2 Time base 1.0 Preset 5 sec Accumulator O T4:2/TT 0:013 YELLOW T4:2/DN T4:0 (RES) OR

# **SUMMER - 16 EXAMINATION**

Subject Code:17664

|            | Imputs I:0/o (Start)                                                  |              |          |

|------------|-----------------------------------------------------------------------|--------------|----------|

|            | 1:0/1 (stop)                                                          |              |          |

|            | Outputs 0:010 (RED LAMP)                                              |              |          |

|            | 0: O/I (GREEN LAMP)                                                   |              |          |

|            | 0: 0/2 (YELLOW LAMP)                                                  |              |          |

|            | I:0/0 I:0/1 TIMER ON DELAY                                            |              |          |

|            | TimerT4:1                                                             |              |          |

|            | Time baseta                                                           |              |          |

|            | Preset 45<br>Acumulatin o                                             |              |          |

|            | LEQ 0:0/0                                                             |              |          |

|            | Source A - O (R)                                                      |              |          |

|            | Source B-15                                                           |              |          |

|            | LIM                                                                   |              |          |

|            | Lower lim-16   O: 0/1                                                 |              |          |

|            | Higher lim-25                                                         |              |          |

|            |                                                                       |              |          |

|            | GRQ 0:0/2                                                             |              |          |

|            | Source A- 26 (Y)                                                      |              |          |

|            | Source B-45                                                           |              |          |

|            |                                                                       |              |          |

|            | TI/DN TI                                                              |              |          |

|            | (RES)                                                                 |              |          |

|            |                                                                       |              |          |

|            |                                                                       |              |          |

|            | OR                                                                    |              |          |

|            | OR                                                                    |              |          |

| 0.0        | Any other relevant ladder diagram shall be considered                 |              | 4.5      |

| Q.3<br>a)  | Attempt any FOUR: State classification of PLC based on type and size. |              | 16<br>04 |

| Ans        | Classification of PLC based on type and size: PLC : -                 | 04           |          |

|            | A) Micro PLC (Fixed I/O)                                              | Marks for    |          |

|            | B) Modular PLC: - i) Small PLC                                        | classificati |          |

|            | ii) Medium<br>iii) Large                                              | on           |          |

| <b>b</b> ) | Enlist any four automation tools used in process. Explain DCS.        |              | 04       |

| Ans        | Automation tools used in process : (Any two)                          | 01 mark      |          |

|            | 1) PLC                                                                | for each     |          |

|            | 2) SCADA                                                              | point        |          |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### **SUMMER - 16 EXAMINATION**

|            | 2) 779 67                                                                                                                                                                                                                                                                                                                  | 1                                         |    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----|

|            | 3) HMI                                                                                                                                                                                                                                                                                                                     |                                           |    |

|            | 4)DCS                                                                                                                                                                                                                                                                                                                      |                                           |    |

|            | 5)CNC                                                                                                                                                                                                                                                                                                                      |                                           |    |

|            | 6)DNC                                                                                                                                                                                                                                                                                                                      |                                           |    |

|            | DCS- Distributed Control System:                                                                                                                                                                                                                                                                                           |                                           |    |

|            | <ul> <li>A distributed control system (DCS) is a control system for a</li> </ul>                                                                                                                                                                                                                                           |                                           |    |

|            | process or plant, wherein control elements are distributed                                                                                                                                                                                                                                                                 | 02 marks                                  |    |

|            | throughout the system.                                                                                                                                                                                                                                                                                                     | for                                       |    |

|            | • This is in contrast to non-distributed systems, which use a single                                                                                                                                                                                                                                                       | explanation                               |    |

|            | controller at a central location. In a DCS, a hierarchy of                                                                                                                                                                                                                                                                 |                                           |    |

|            | controllers is connected by communications networks for                                                                                                                                                                                                                                                                    |                                           |    |

|            | command and monitoring                                                                                                                                                                                                                                                                                                     |                                           |    |

| <b>c</b> ) | Give specifications of AC and DC input modules (2 each).                                                                                                                                                                                                                                                                   |                                           | 04 |

| Ans        | Specification of AC i/p module at rated 120V AC: (Any two)                                                                                                                                                                                                                                                                 | 01 marks                                  | 04 |

| 11113      | 1)Input per module-32(8 group of four)                                                                                                                                                                                                                                                                                     | for each                                  |    |

|            | 2) Voltage range- 85 to 135 Vac , 50/60 Hz                                                                                                                                                                                                                                                                                 | specificatio                              |    |

|            | 3) I/P voltage -120Vac                                                                                                                                                                                                                                                                                                     | n                                         |    |

|            | 4) I/p current- 8.8 ma@ 115v,50Hz                                                                                                                                                                                                                                                                                          | "                                         |    |

|            | 5)Minimum on state <u>current- 4.2ma @85Vac, 50Hz</u>                                                                                                                                                                                                                                                                      |                                           |    |

|            | 6)Minimum off state current- 1.9ma@30Vac,50Hz                                                                                                                                                                                                                                                                              |                                           |    |

|            | 7) Power dissipation-4.5w(max),1.0w(min)                                                                                                                                                                                                                                                                                   |                                           |    |

|            | Specification of DC i/p module at rated 24V DC: (Any two)  1) Rated voltage and current - +24V DC at 4mA  2) Specified operational voltage range - 0- +30V DC  3) Absolute maximum i/p voltage- +35V DC for 0.5 sec.  4) Signal Delay -5 millisecond (ON to OFF or OFF to ON)  5) Input power – 0.2 Watts/point at 24V DC. | 01 marks<br>for each<br>specificatio<br>n |    |

|            | OR                                                                                                                                                                                                                                                                                                                         |                                           |    |

|            | Any other relevant specification shall be considered                                                                                                                                                                                                                                                                       |                                           |    |

| d)         | For timer instruction, if addressing is                                                                                                                                                                                                                                                                                    |                                           | 04 |

| Ans        | T4: 1/DN, what does T4, :, 1, / and DN indicates.                                                                                                                                                                                                                                                                          |                                           |    |

| 71113      | T4:1/DN,                                                                                                                                                                                                                                                                                                                   |                                           |    |

|            | This bit indicates                                                                                                                                                                                                                                                                                                         | 01 mark                                   |    |

|            | This of indicates                                                                                                                                                                                                                                                                                                          | For each                                  |    |

|            | T4 = timer file no.4,                                                                                                                                                                                                                                                                                                      | point                                     |    |

|            | 1 = timer 1 ,it stores timer information                                                                                                                                                                                                                                                                                   | (4 marks                                  |    |

|            | : =Element Delimiter                                                                                                                                                                                                                                                                                                       | maximum)                                  |    |

|            | / = Bit Delimiter                                                                                                                                                                                                                                                                                                          |                                           |    |

|            | $\mathbf{DN} = \text{Done bit}$                                                                                                                                                                                                                                                                                            |                                           |    |

| e)         | Enlist any four parameters to be considered while PLC installation.                                                                                                                                                                                                                                                        |                                           | 04 |

| Ans        | Describe grounding.                                                                                                                                                                                                                                                                                                        | 01 marks                                  |    |

| 11113      | Parameters to be considered while PLC installation: (Any two)                                                                                                                                                                                                                                                              | for each                                  |    |

|            | r arameters to be considered while recomstaliation. (Any two)                                                                                                                                                                                                                                                              | point                                     |    |

|            |                                                                                                                                                                                                                                                                                                                            | Pome                                      | 1  |

## **SUMMER - 16 EXAMINATION**

|            | <ul> <li>Verify safety circuits correctly in PLC applications to protect</li> </ul>                                                      |                       |          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|

|            | people and equipment                                                                                                                     |                       |          |

|            | <ul> <li>Prevent noise, heat, and voltage variations from ruining your<br/>PLC</li> </ul>                                                |                       |          |

|            | System                                                                                                                                   |                       |          |

|            | <ul> <li>Implement a step-by-step static and dynamic start-up checkout<br/>to</li> </ul>                                                 |                       |          |

|            | guarantee smooth PLC system operation                                                                                                    |                       |          |

|            | <ul> <li>Verify that all I/O wiring connections at the controller end are in<br/>place and securely terminated.</li> </ul>               |                       |          |

|            | Inspect all CPU components and I/O modules to ensure that they are                                                                       |                       |          |

|            | installed in the correct slot locations and placed securely in                                                                           |                       |          |

|            | position                                                                                                                                 |                       |          |

|            | <ul> <li>Visually inspect the system to ensure that all PLC hardware<br/>compo-</li> </ul>                                               |                       |          |

|            | nents are present. Verify correct model numbers for each                                                                                 |                       |          |

|            | <ul><li>component</li><li>Easy accessible of PLC for maintenance</li></ul>                                                               |                       |          |

|            |                                                                                                                                          |                       |          |

|            | Grounding: Proper grounding is an important safety measure in all electrical                                                             |                       |          |

|            | installations. The authorative source on grounding requirements for a                                                                    |                       |          |

|            | PLC installation is the National Electrical Code. The code specifies the                                                                 | 02 marks              |          |

|            | type of conductors, color codes, and connections necessary for safe                                                                      | for                   |          |

|            | grounding of electrical components. According to the code, the                                                                           | description           |          |

|            | grounding path must be permanent (no solder), continuous, and able to conduct safely the ground-fault current in the system with minimal |                       |          |

|            | impedance. In the event of a high value of ground current, the                                                                           |                       |          |

|            | temperature of the conductor could cause the solder to melt, resulting in                                                                |                       |          |

|            | interruption of the ground connection. In addition to the grounding                                                                      |                       |          |

|            | required for the controller and its enclosure, you must also provide                                                                     |                       |          |

| 0.4.1      | proper grounding for all controlled devices in application.                                                                              |                       | - 10     |

| Q.4 A)     | Attempt any THREE:                                                                                                                       |                       | 12<br>04 |

| <b>a</b> ) | Draw functional block of on- delay timer instruction, state function of  (i) Enable bit (EN)                                             |                       | U4       |

|            | (ii) Done bit (DN)                                                                                                                       |                       |          |

|            | (iii) Timing bit (TT)                                                                                                                    |                       |          |

| Ans        | ON Delay timer:                                                                                                                          | 01 mark for<br>format |          |

|            |                                                                                                                                          |                       |          |

|            |                                                                                                                                          |                       |          |

|            |                                                                                                                                          |                       |          |

Subject Code: 17664

### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **SUMMER - 16 EXAMINATION**

**Model Answer**

1:010/5 Timer on Delay Timer T4:0 Timer Base 1.0 Preset 5 Accumulator 0 T4:0/TT T4:0/DN OR Any other relevant functional block shall be considered **Functions of parameters:** 01 mark i)EN: Enable bit-This bit is set, when input to timer is true. Indicates timer operation has begun. ii) DN: Done bit-This bit is set, when accumulator value becomes equal to 01 mark preset value and then respective output becomes ON. Indicates timing operation is complete. iii) TT: Timer timing bit- This bit is set when timer is running. Indicates 01 mark timing operation is running Describe term Redundancy, list its types. 04 b) Ans **Description of Redundancy:** Redundancy means extra system components or mechanisms 03 added to decrease the chance of total system failure. marks for Different types of redundancy are available in PLC like description redundancy for a CPU module, power module, bases and communication module is available. CPU redundancy system is composed of separate bases for ideal redundancy structure. In case an error occurs in an active CPU module, a backup module is automatically converted to active one for continuous operation. In these cases two processors can be tied into one I/O system and some means is provided that switches control from the failure CPU to the backup when a failure CPU to the backup when a failure occurs as shown in Fig.

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **SUMMER - 16 EXAMINATION**

Subject Code: 17664

### **Model Answer**

Switchover CPU 1 To 4O The working of total system is reliability of its operation. The safety of critical load is increased by transferring it from a failed power module to an alternative source of power. Thus, reliability can be increased by selective use of redundancy. Types of Redundancy:i)Redundancy for CPU 01 mark for ii) Redundancy Power supply module list iii) Redundancy for basic and communication module OR a)Hot Redundancy b)Warm Redundancy c) Cold Redundancy OR 1) Separate mode 2) Shadow mode 3) Split mode 4) Voting mode 04 c) Draw symbol, Boolean equation, electrical and ladder diagram from given truth table. Input **Output** В Y A 0 0 0 1 1 1 0 1 1 1 0 Ans

**SUMMER - 16 EXAMINATION**

**Model Answer**

Subject Code:17664

| Two i/pEX-OR Gate (Symbol)  * Boolean equation for given that table.  Y = A·B + A·B  * electrical diagram:  A + B  Too Load  * Ladder diagram for given T.T.  A B  Hall Hall D  A T B  Too Load  * Ladder diagram for given T.T.                                                                                                                                                                                                                                                                                                                      | 01 marks for Boolean equation  01 mark for electrical diagram  01 mark for ladder diagram                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| What are the guidelines to maintain PLC in good running condition?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     | 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Guidelines for maintenance of PLC: (Any four)  1) Periodically check the tightness of I/O Module terminal screws. They can became loose over period  2) Periodically check for corrosion of connecting terminals. moisture & corrosion atmospheres can cause porr electrical connections  3) Replace the PLC batteries used for backup in time  4) Have a written check list, control list for each PLC  5)Make sure that components are free of dust  6) Stock commonly needed spare parts  7) Keep duplicate record of operating programs being use | 01<br>marks for<br>each<br>point                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | * Bolean equation for given truth troke.  Y = A·B + A·B  * electrical langram  * Ladder langram for given T.T.    B | * Boolean equation for given truth table.  Y = A · B + A · B  * electrical diagram  * Ladder diagram for given T.T.  What are the guidelines to maintain PLC in good running condition?  Guidelines for maintenance of PLC: (Any four)  1) Periodically check the tightness of I/O Module terminal screws. They can became loose over period  2) Periodically check for corrosion of connecting terminals. moisture & corrosion atmospheres can cause porr electrical connections  3) Replace the PLC batteries used for backup in time  4) Have a written check list, control list for each PLC  5)Make sure that components are free of dust  6) Stock commonly needed spare parts |

# **SUMMER - 16 EXAMINATION**

| Q.4 B) | Attempt any ONE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               | 06 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----|

| a)     | Explain the term 'speed of execution' with proper example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               | 06 |

| Ans    | <ul> <li>This is one of the characteristics of PLC "Speed at PLC scans memory and executes instructions is speed of execution" <ul> <li>A period between one I/O update and the next is termed as "One scan"</li> <li>Time taken by PLC to update one of I/O terminal is Scan time</li> <li>Scan time is generally measured in msec.</li> <li>Speed of execution depends on speed of CPU, length of ladder diagram, types of instruction used in program.</li> <li>Slower the CPU speed or longer the ladder diagram, takes more time to execute the program</li> </ul> </li> </ul> | 03 marks<br>for<br>description                |    |

| b)     | <ul> <li>For example.</li> <li>In AB SLC 500 PLC</li> <li>For execution of XIO, XIC takes 4 microsecond for true and false of instruction</li> <li>But for OTE instruction 18 microsecond are required</li> <li>If ladder diagram is with XIC, OTE then total time required to execute the program is 22 microsecond</li> </ul>                                                                                                                                                                                                                                                     | 03 marks<br>for<br>example                    | 06 |

| b) Ans | Describe criteria on which input/output modules are selected.  Criteria's for selection of I/O module: (any six)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 01 mark for                                   | 06 |

|        | <ul> <li>Number of analog and digital inputs</li> <li>Numbers of analog and digital outputs</li> <li>Type of isolation in I/O module</li> <li>Sourcing and sinking type of I/O terminals</li> <li>DC voltage and current ratings for discrete i/p modules</li> <li>DC voltage and current ratings for discrete o/p modules</li> <li>Resolution of analog i/p module</li> <li>Resolution of analog o/p module</li> <li>Power supply voltage</li> <li>Type of I/O signals –temperature, pressure, speed control etc</li> </ul>                                                        | each<br>point                                 |    |

| Q.5    | Attempt any TWO:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               | 16 |

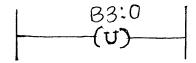

| a)     | Draw neatly and explain sourcing and sinking I/O modules in detail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 021.                                          | 08 |

| Ans    | Sourcing output module:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 02 marks<br>for<br>sourcing<br>o/p<br>module. |    |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **SUMMER - 16 EXAMINATION**

**Model Answer**

Subject Code: 17664

Fig -Sourcing o/p module interface to field devices.

The interface diagram of PLC as output module is shown in above fig. In operation with PLC as sourcing output module, current from positive terminal of power supply flows first from output module to output device and then to common terminal so the output module acts as source of current for output devices.

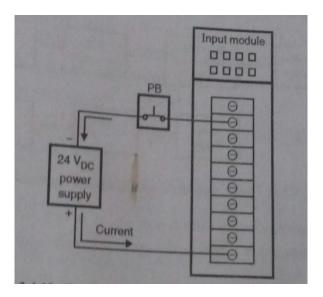

### **Sourcing input module:**

The interface diagram of PLC input module as sourcing is shown in figure. In operation ,PLC input module as sourcing, current from power supply first flows from input module to load and then to common terminal so the input module acts as source of current.

02 marks for sourcing i/p module.

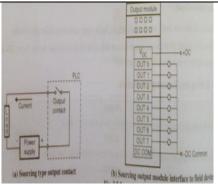

**Sinking Output Module:**

Subject Code: 17664

### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **SUMMER - 16 EXAMINATION**

**Model Answer**

0000 02 marks OUT 3 for sinking OUT 4 o/p OUT 5 module. OUT 6 -0-OUT 7 -0--DC Common inking output module interface to field devices Figure, Shows sinking o/p module where current from positive terminal of DC power supply flows first from o/p device to o/p module and then to common terminal. So here, output module is sinking current from output device so it is sinking output module. **Sinking Input Module:** Input module 0000 0000 02 marks for sinking i/p module power supply Figure, Shows sinking i/p module where current from positive terminal of DC power supply flows first from i/p device to i/p module and then to common terminal. So here, input module is sinking current from input device so it is sinking input module. (i) Enlist four advantages of ladder programming. 08 b) (ii) Write PLC ladder program to measure frequency of events using

### **SUMMER - 16 EXAMINATION**

Subject Code:17664