(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

# **MODEL ANSWER**

### **WINTER-17 EXAMINATION**

# Subject Title: Very Large Scale Integration

Subject Code:

17659

<u>Important Instructions to examiners:</u>

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for anyequivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

For programming language papers, credit may be given to any other program based on equivalent concept

| Q.<br>No. | Sub<br>Q.N. | Answer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Marking<br>Scheme                |

|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Q.1       | A)          | Attempt any three:                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12-Total<br>Marks                |

|           | a)          | Write VHDL program for 3 bit up counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4M                               |

|           | Ans:        | library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;  entity Counter_3bit is    Port ( CLK : in STD_LOGIC;         Count : out STD_LOGIC_VECTOR (2 downto 0)); end Counter_3bit;  architecture Behavioral of Counter_3bit is         signal cin : std_logic_vector(2 downto 0) :="000"; begin         process(CLK)         begin         if(rising_edge(CLK)) then         if(cin = "111") then         cin<= "000";         else         cin<= cin + 1;         end if; | Entity-1M,<br>Architecture<br>3M |

|           |             | end if;  Count <= cin; end process; end Behavioral;                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  |

|            | <u>OR</u>                                                                                            |         |

|------------|------------------------------------------------------------------------------------------------------|---------|

|            | signal cin : std_logic_vector(2 downto 0) :="000";                                                   |         |

|            | begin                                                                                                |         |

|            | process(CLK)                                                                                         |         |

|            | begin                                                                                                |         |

|            | if (CLK= '1' and CLK'event) then                                                                     |         |

|            | $cin \le cin + 1;$                                                                                   |         |

|            | end if;                                                                                              |         |

|            | Count <= cin;                                                                                        |         |

|            | end process;                                                                                         |         |

|            | end Behavioral;                                                                                      |         |

| <b>b</b> ) | Define the terms:                                                                                    | 4M      |

|            | i) Noise margin                                                                                      |         |

|            | ii) Skew.                                                                                            |         |

| Ans:       |                                                                                                      | 2M      |

|            | Only definition is expected correct definition of each carries 2 Marks                               |         |

|            | Noise Margin:                                                                                        |         |

|            | Noise margin is the amount of noise that a CMOS circuit could withstand without                      |         |

|            | compromising the operation of circuit.                                                               |         |

|            | <u>OR</u>                                                                                            |         |

|            | It is a measure of noise immunity of a gate or circuit (noise immunity is the ability of a gate      |         |

|            | or circuit to tolerate any noise present in a signal without performing a wrong operation).          |         |

|            | Skew:                                                                                                |         |

|            | The clock signal, which is said to be applied simultaneously to all the flip-flops, may cause a      | 2M      |

|            | minute delay changes due to some variation in the wiring between the components. Due to this, it     | 2111    |

|            | may happen that the clock signal may arrive at the clock inputs of different flip-flops at different |         |

|            | times. This delay is termed as skew.                                                                 |         |

|            | OR                                                                                                   |         |

|            | The difference in the clock arrival time is call clock skew.                                         |         |

|            | $\underline{\mathbf{OR}}$                                                                            |         |

|            | In circuit designs, <b>clock skew</b> (sometimes called <b>timing skew</b> ) is a phenomenon         |         |

|            | in synchronous circuits in which the clock signal (sent from the clock circuit) arrives at           |         |

|            | different components at different times.                                                             |         |

| c)         | State the use and syntax of:                                                                         | 4M      |

| -          | i) Signal                                                                                            |         |

|            | ii) Constant.                                                                                        |         |

| Ans:       | Signal: Signals are communication media between entities. Signals are nothing but wires              | 2M each |

|            | which connect two or more components lying inside IC. Signals can be declared in package             |         |

|            | can be shared among entities and are called global signals. Signals hold a list of values which      |         |

|            | includes the current value of the signal and a set of possible future values that are to appear      |         |

|            | on the signal. Signal objects are used to connect entities together to form models.                  |         |

|            | Signals declared in any entity declaration section are global to any architecture for that           |         |

|            | entity. Signals declared in architecture can only be referenced in that architecture only.           |         |

|            | <b>Syntax</b> : Signal signal_name :signal type := initial value.                                    |         |

|            | <b>Constant:</b> Constant objects are names assigned to specific values of a type. Constant is an    |         |

|            |                                                                                                      |         |

|            | object in VHDL whose value cannot be changed once defined for the design. By use of constant model becomes readable and easy to update. A single value of a given type is assigned to the constant before simulation starts and this value cannot be changed during simulation.  Syntax: Constant constant_name: type_name := value.  Note: initial value if any                                                                                                                                                                                                                                                                                                                                                                    |                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| <b>d</b> ) | Draw two input NAND gate using CMOS technology. Write its truth table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4M             |

| Ans:       | <u>Diagram-</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2M             |

|            | $A \circ \bigcap_{Y = AB} T_3$ $Y = AB$ NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

|            | Truth table-           A         B         T1         T2         T3         T4         Y           0         0         OFF         OFF         ON         ON         Vdd           0         Vdd         ON         OFF         ON         OFF         Vdd           Vdd         0         OFF         ON         OFF         ON         Vdd           Vdd         Vdd         ON         ON         OFF         OFF         O                                                                                                                                                                                                                                                                                                      | Truth table 2M |

| e)         | Explain efficient coding style.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4M             |

| Ans:       | <ul> <li>A coding style is set of rules that a programmer uses for choosing an expressive form to use in the given situation.</li> <li>There may be more than one method to model a particular design part but only a few would yield better performance.</li> <li>The essence of VHDL coding lies in understanding which style yields the ultimate performance under the given set of specifications.</li> <li>The key to higher performance is to avoid writing code that needlessly creates additional work for the HDL compiler and synthesizer, which, in turn, generates designs with greater number of gates.</li> <li>Basically, any coding style that gives the HDL simulator information about the design that</li> </ul> | 4M             |

|            | cannot be passed onto the synthesis tool is a bad coding style.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _          |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

|            | Rules:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |  |  |  |  |

|            | 1. Use optimised standard libraries: The performance is increased when standard libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |

|            | are used instead of unoptimized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |  |  |  |  |

|            | 2. Reduce process sensitivity: this will prevent the function getting unnecessarily and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |  |  |  |  |

|            | repeatedly executed.  3. Reducing waits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |

|            | 4. Reduce delay calculations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |  |  |  |  |

|            | 5. Integers vs. Vectors: To increase the performance ranged integers are used in entity instead of std_logic_vectors. The simulator may be able to process the design faster and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |  |  |  |  |

|            | efficiently. 6. Optimize everything above 1%: The performance analyser will identify the lines of code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |  |  |  |  |

|            | that consumes the greatest CPU time and display these lines in order in the performance profile window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |  |  |  |  |

| D)         | Calva any ana t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12-Total   |  |  |  |  |

| <b>B</b> ) | Solve any one:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Marks      |  |  |  |  |

| ı)         | Explain different level of simulation in brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6M         |  |  |  |  |

| Ans:       | • Behavioural Simulation: Behavioural simulation employs a high level of abstraction to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1M each    |  |  |  |  |

|            | model the decidn. And also timing aspects are considered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |

|            | model the design. And also timing aspects are considered. <b>Ex:</b> f <=a and b after ns;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |  |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |  |  |  |  |

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |  |  |  |  |

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |  |  |  |  |

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |  |  |  |  |

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation: It requires transistor models. The circuit is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |  |  |  |  |

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation.</li> <li>Transistor level or circuit level simulation: It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  |            |  |  |  |  |

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation.</li> <li>Transistor level or circuit level simulation: It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of mathematical equations relating current and voltage is set up and solved by numerical</li> </ul>                                                                                                                                                                                                                                                                            |            |  |  |  |  |

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation.</li> <li>Transistor level or circuit level simulation: It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of mathematical equations relating current and voltage is set up and solved by numerical techniques. It requires data structures and large amount of computing resources and gives</li> </ul>                                                                                                                                                                                  |            |  |  |  |  |

| •)         | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation.</li> <li>Transistor level or circuit level simulation: It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of mathematical equations relating current and voltage is set up and solved by numerical techniques. It requires data structures and large amount of computing resources and gives analog results. It is the most accurate method. The frequency response can also be computed.</li> </ul>                                                                                     | 6M         |  |  |  |  |

| <b>)</b>   | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation.</li> <li>Transistor level or circuit level simulation: It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of mathematical equations relating current and voltage is set up and solved by numerical techniques. It requires data structures and large amount of computing resources and gives</li> </ul>                                                                                                                                                                                  | 6M         |  |  |  |  |

| )          | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation:  Transistor level or circuit level simulation: It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of mathematical equations relating current and voltage is set up and solved by numerical techniques. It requires data structures and large amount of computing resources and gives analog results. It is the most accurate method. The frequency response can also be computed.</li> <li>Explain following statement with example: i) Process statement it) Wait statement.</li> </ul> |            |  |  |  |  |

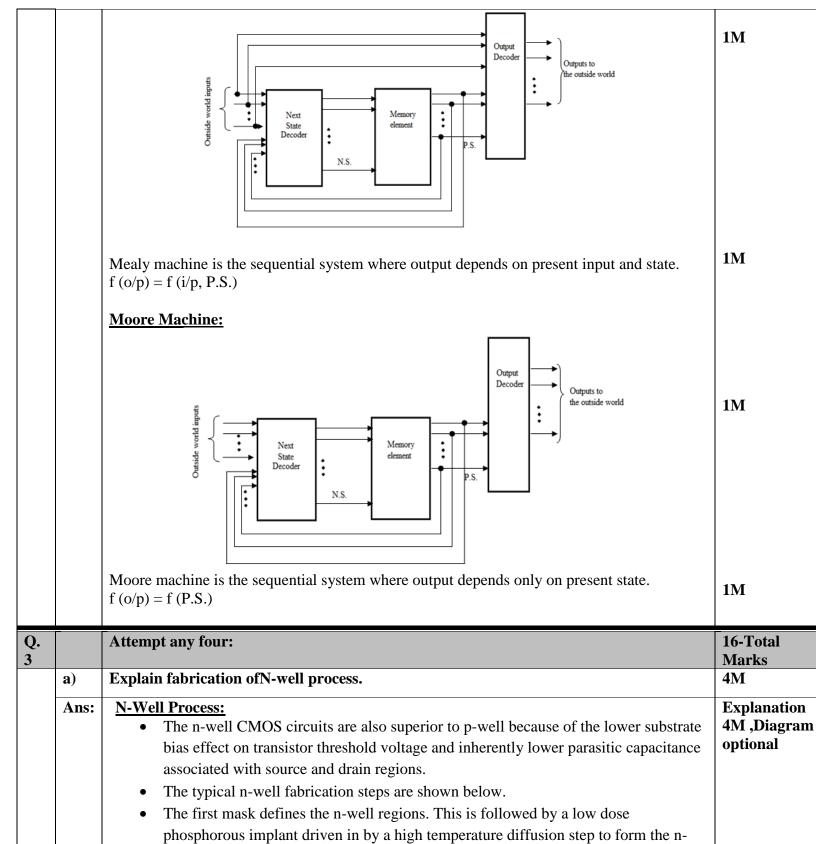

|            | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation:  It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of mathematical equations relating current and voltage is set up and solved by numerical techniques. It requires data structures and large amount of computing resources and gives analog results. It is the most accurate method. The frequency response can also be computed.</li> <li>Explain following statement with example:  i) Process statement: Process statement is the primary mechanism used in sequential</li> </ul>   | 6M 3M Each |  |  |  |  |

| o)<br>Ans: | <ul> <li>Ex: f &lt;=a and b after ns;</li> <li>Functional simulation: It ignores the timing aspects of the circuit and verifies only the functionality of the design.</li> <li>Static timing analysis: It has a built in tool that computes delay for each timing path. It does not require input stimuli. The reports are generated after simulation.</li> <li>Gate level simulation: It is used to check the timing performance of a design. The delay parameters of logic cells are used to verify timings.</li> <li>Switch level simulation: It is one level below the gate level simulation. It models transistors which are used in gates as switches. It provides more accurate timing predictions than the gate level simulation:  Transistor level or circuit level simulation: It requires transistor models. The circuit is described in terms of resistances, capacitances, voltages and current sources. A set of mathematical equations relating current and voltage is set up and solved by numerical techniques. It requires data structures and large amount of computing resources and gives analog results. It is the most accurate method. The frequency response can also be computed.</li> <li>Explain following statement with example: i) Process statement it) Wait statement.</li> </ul> |            |  |  |  |  |

# MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

any of the signals in the sensitivity list, the statements within the process is executed. Inside the process the execution of statements will be sequential and if one entity is having two processes the execution of these processes will be concurrent. At the end it waits for another event to occur.

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

use IEEE.STD LOGIC UNSIGNED.ALL;

entity Counter 3bit is

Port ( CLK : in STD_LOGIC;

Count: out STD LOGIC VECTOR (2 downto 0));

end Counter_3bit;

architecture Behavioral of Counter_3bit is

signal cin: std_logic_vector(2 downto 0) :="000";

begin

process(CLK)

begin

if (CLK='1' and CLK'event) then

cin \le cin + 1:

end if:

Count <= cin;

end process;

end Behavioral;

```

### ii) Wait Statements:

wait: statement suspends the execution of a process or procedure until some conditions are met.

```

wait on [sensitivity list]; eg. wait on clk;

```

```

wait until [condition]; wait until clk='1'' wait for [time out expression]; wait for 20 ns;

```

# OR

Wait statements put the process execution on hold until the specified condition is fulfilled. If no condition is given, the process will never be reactivated again.

Wait statements must not be combined with a sensitivity list, independent from the application field. Wait statement stop the process execution. The Process is continued when the instruction is fulfilled

### **Different types of wait statement:**

- ➤ Wait for a specific time: wait for SPECIFIC\_TIME;

- ➤ Wait for a signal event: wait on SIGNAL\_LIST;

- ➤ Wait for a true condition (requires an event): wait until CONDITION;

|      | <b>Exampl</b>                   | <u>e:</u>                                                                                                                   |               |                                                                                                                                                                             |              |  |

|------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|

|      | entity I                        |                                                                                                                             | :             |                                                                                                                                                                             |              |  |

|      | p<br>bit;                       | ort(D, CLK :                                                                                                                | in            |                                                                                                                                                                             |              |  |

|      | on,                             | Q : 0                                                                                                                       | out           |                                                                                                                                                                             |              |  |

|      | bit);                           |                                                                                                                             | out           |                                                                                                                                                                             |              |  |

|      | end FF                          | ,                                                                                                                           |               |                                                                                                                                                                             |              |  |

|      |                                 | cture BEH1 of FF is                                                                                                         |               |                                                                                                                                                                             |              |  |

|      | begin                           |                                                                                                                             |               |                                                                                                                                                                             |              |  |

|      | proce<br>begin                  | SS                                                                                                                          |               |                                                                                                                                                                             |              |  |

|      | _                               | on CLK;                                                                                                                     |               |                                                                                                                                                                             |              |  |

|      |                                 | LK = '1') then                                                                                                              |               |                                                                                                                                                                             |              |  |

|      |                                 | Œ D;                                                                                                                        |               |                                                                                                                                                                             |              |  |

|      | end                             |                                                                                                                             |               |                                                                                                                                                                             |              |  |

|      |                                 | ocess;                                                                                                                      |               |                                                                                                                                                                             |              |  |

| ,    | end BE                          | ·                                                                                                                           |               |                                                                                                                                                                             | 12-Tota      |  |

|      | Attempt any two:                |                                                                                                                             |               |                                                                                                                                                                             |              |  |

| a)   | Differe                         | tiate between BJT and Cl                                                                                                    | MOS.          |                                                                                                                                                                             | Marks<br>4 M |  |

| Ans: |                                 |                                                                                                                             |               |                                                                                                                                                                             | Any 4 p      |  |

|      | Sr.                             | Bipolar Junction T                                                                                                          | ransistor     | Complementary Metal Oxide                                                                                                                                                   | 1M each      |  |

|      | No.                             | Dipoliti o time tion 11                                                                                                     |               | Semiconductor                                                                                                                                                               |              |  |

|      |                                 |                                                                                                                             |               |                                                                                                                                                                             |              |  |

|      | 1                               | BJT junctions are emitter base                                                                                              | e and         |                                                                                                                                                                             |              |  |

|      |                                 | BJT junctions are emitter base collector                                                                                    | e and         | CMOS junctions are gate, source, drain and substrate                                                                                                                        |              |  |

|      |                                 | collector                                                                                                                   | e and         | CMOS junctions are gate, source, drain and substrate                                                                                                                        |              |  |

|      | 1                               |                                                                                                                             | e and         | CMOS junctions are gate, source, drain and                                                                                                                                  |              |  |

|      | 2                               | collector  LOW power applications                                                                                           | e and         | CMOS junctions are gate, source, drain and substrate High power applications                                                                                                |              |  |

|      | 2 3                             | collector  LOW power applications  Bipolar device                                                                           | e and         | CMOS junctions are gate, source, drain and substrate High power applications Unipolar Device                                                                                |              |  |

|      | 1<br>2<br>3<br>4                | collector  LOW power applications  Bipolar device  Low input Impedance                                                      | e and         | CMOS junctions are gate, source, drain and substrate  High power applications  Unipolar Device  High Input Impedance                                                        |              |  |

|      | 1<br>2<br>3<br>4<br>5           | collector  LOW power applications  Bipolar device  Low input Impedance  Low current gain                                    | e and         | CMOS junctions are gate, source, drain and substrate High power applications Unipolar Device High Input Impedance High Current gain                                         |              |  |

|      | 1<br>2<br>3<br>4<br>5<br>6      | collector  LOW power applications  Bipolar device  Low input Impedance  Low current gain  More fan out                      |               | CMOS junctions are gate, source, drain and substrate  High power applications  Unipolar Device  High Input Impedance  High Current gain  Less fan out                       |              |  |

|      | 1<br>2<br>3<br>4<br>5<br>6<br>7 | collector  LOW power applications  Bipolar device  Low input Impedance  Low current gain  More fan out  Low packing density | ves rise to a | CMOS junctions are gate, source, drain and substrate  High power applications  Unipolar Device  High Input Impedance  High Current gain  Less fan out  High Packing density |              |  |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

|      | Explanation-                                                                                                                                                              | 2M          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

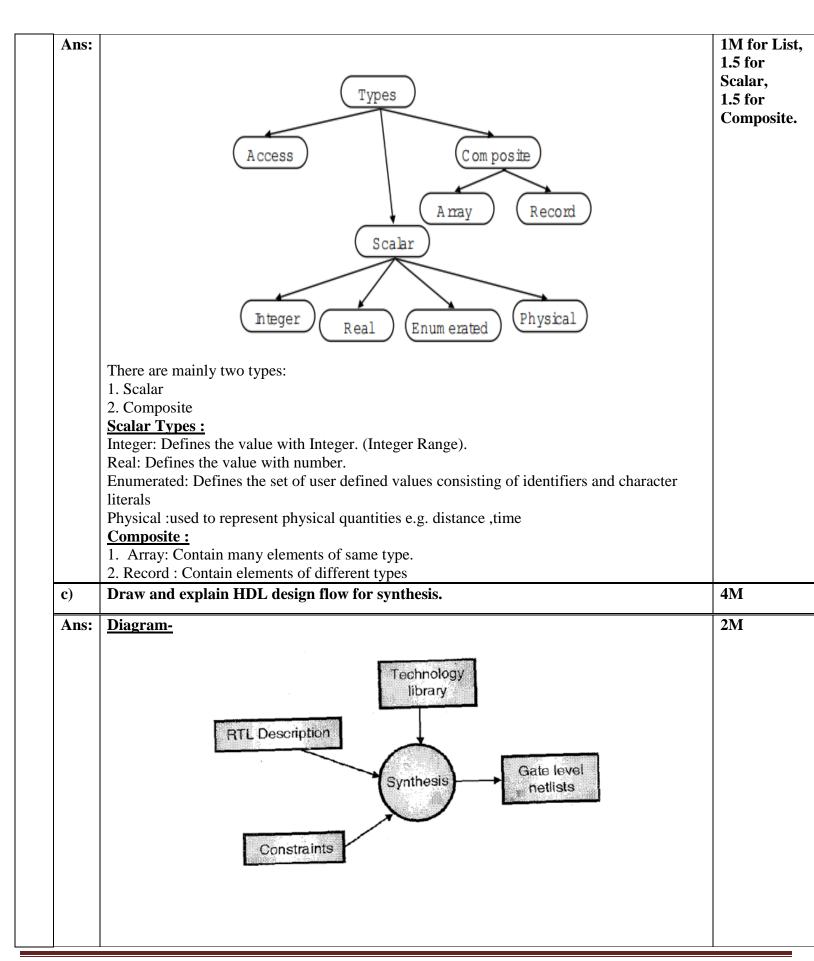

|      | HDL Design flow for Synthesis:                                                                                                                                            |             |

|      | • To convert RTL (register description to gates), there are three steps as under:                                                                                         |             |

|      | 1. Translation                                                                                                                                                            |             |

|      | 2. Boolean Optimization                                                                                                                                                   |             |

|      | 3. Optimization                                                                                                                                                           |             |

|      | 1. Translation:                                                                                                                                                           |             |

|      | <ul> <li>RTL description is translated to un-optimized Boolean description usually with<br/>primitive gates like AND and OR gates, and flip-flops and latches.</li> </ul> |             |

|      | RTL description to Boolean equivalent circuit is not controlled by user.                                                                                                  |             |

|      | 2. Boolean Optimization:                                                                                                                                                  |             |

|      | Algorithms are executed on the Boolean optimized description.                                                                                                             |             |

|      | 3. Optimization:                                                                                                                                                          |             |

|      | Optimization process takes an unoptimization Boolean description.                                                                                                         |             |

|      | Optimization uses number of algorithms to convert unoptimizes Boolean descriptions                                                                                        |             |

|      | to a very low level description (PLC format).                                                                                                                             |             |

|      | • Thus, when we optimize 'PLA Format', we get description. We have to reduce the                                                                                          |             |

|      | logic generated by sharing common terms.                                                                                                                                  |             |

|      | Optimized Boolean equivalent description is mapped to actual logic gates by making                                                                                        |             |

|      | use of technology library of target process.                                                                                                                              |             |

|      | <u>OR</u>                                                                                                                                                                 |             |

|      | 1. Describe your design with HDL                                                                                                                                          |             |

|      | 2. Perform RTL simulation                                                                                                                                                 |             |

|      | 3. Synthesizing your design                                                                                                                                               |             |

|      | 4. Create Xilinx Netlist Files (XNF/EDIF etc)                                                                                                                             |             |

|      | 5. Perform Functional Simulation                                                                                                                                          |             |

|      | 6. Floor planning of design (optional)                                                                                                                                    |             |

|      | 7. Placing and routing                                                                                                                                                    |             |

|      | 8. Perform a timing simulation (post layout)                                                                                                                              |             |

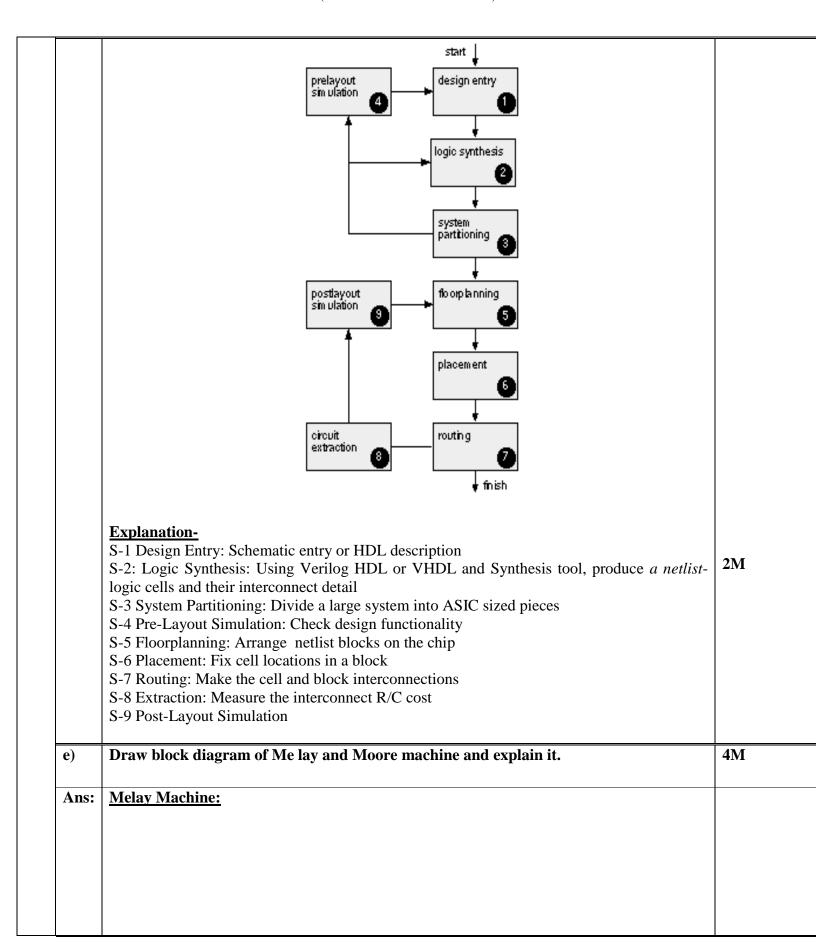

| l)   | Draw ASIC design flow and explain it.                                                                                                                                     | 4M          |

| ns:  | Diagram-                                                                                                                                                                  | 2M          |

| 11J+ | 2-2-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1                                                                                                                                   | <b>2171</b> |

|      |                                                                                                                                                                           |             |

|      |                                                                                                                                                                           |             |

|      |                                                                                                                                                                           |             |

|      |                                                                                                                                                                           |             |

|      |                                                                                                                                                                           | 1           |

# MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

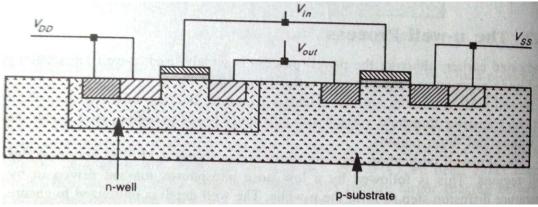

well.

# MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

The well depth is optimized to ensure against p-substrate to p+ diffusion breakdown

without compromising the n-well to n+ mask separation.

# MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

• The next steps are to define the devices and diffusion paths, grow field oxide, deposit and pattern the polysilicon, carry out the diffusion, make contact cuts and finally metallise.

# <u>OR</u>

- Thick SiO2 layer is grown on p-type silicon wafer.

- After defining the area for N-well diffusion, using a mask, the SiO2 layer is etched off and n-well diffusion process is carried out.

- Oxide in the n transistor region is removed and thin oxide layer is grown all over the surface to insulate gate and substrate.

- The polysilicon is deposited and patterned on thin oxide regions using a mask to form gate of both the transistors. The thin oxide on source and drain regions of both the transistors is removed by proper masking steps.

- Using n+ mask and complementary n+ mask, source and drain of both nMOS and pMOS transistors are formed one after another using respective diffusion processes. These same masks also include the VDD and VSS contacts.

- The contacts are made using proper masking procedure and metal is deposited and patterned on the entire chip surface.

- An overall passivation layer is formed and the openings for accessing bonding pads are defined.