# MODEL ANSWER

## SUMMER-17 EXAMINATION

Subject Code:

| 1 | 7650 |  |

|---|------|--|

|   | 1033 |  |

# Subject Title: Very Large Scale Integration

- Important Instructions to examiners:

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for anyequivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q.N. | Answer                                                                                                                                                           | Marking<br>Scheme |

|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Q.1       | ~~~~        | Attempt any THREE :                                                                                                                                              | 12M               |

| <u>x.</u> | i)          | Define :                                                                                                                                                         | 4M                |

|           | ŕ           | 1)Asynchronous sequential circuit                                                                                                                                |                   |

|           |             | 2)Noise margin                                                                                                                                                   |                   |

|           |             | 3)Fan out                                                                                                                                                        |                   |

|           |             | 4)Skew.                                                                                                                                                          |                   |

|           | Ans:        | Asynchronous Sequential Circuit:                                                                                                                                 | 1M                |

|           |             | Asynchronous is wherein all the flip-flops within the counter do not change state                                                                                |                   |

|           |             | simultaneously. This is because all the flip-flops are not clocked simultaneously.                                                                               | 13.5              |

|           |             | Noise Margins:                                                                                                                                                   | 1 <b>M</b>        |

|           |             | It is a measure of noise immunity of a gate or circuit (noise immunity is the ability                                                                            |                   |

|           |             | of a gate or circuit to tolerate any noise present in a signal without performing a                                                                              |                   |

|           |             | wrong operation).                                                                                                                                                |                   |

|           |             | Fan-Out:                                                                                                                                                         | 1M                |

|           |             | It is the maximum number of load gates that can be connected at output without<br>loading with same IC family and by maintaining its output within the specified |                   |

|           |             | limit,                                                                                                                                                           |                   |

|           |             | Skew (Clock Skew):                                                                                                                                               |                   |

|           |             | skew is defined as "the magnitude of the time difference between two events that ideally                                                                         |                   |

|           |             | would occur simultaneously.                                                                                                                                      | 1 <b>M</b>        |

|           | ii)         | Write any two pro's and any two con's of VHDL.                                                                                                                   | <b>4</b> M        |

|           | Ans:        | Pros :                                                                                                                                                           | (1M-              |

|           |             | • Strongly typed language:                                                                                                                                       | Any two           |

|           |             | • Dealing with signed and unsigned numbers is natural, and there's less chance of                                                                                | pros and          |

|           |             | making a precision mistake or assigning a 16-bit signal to a 4-bit signal.                                                                                       | cons)             |

|           |             | Ability to define custom types:                                                                                                                                  | <u> </u>          |

|      | <ul> <li>A VHDL state machine can be coded naturally using the actual state names (e.g. wait, acknowledge, transmit, receive, etc.), not binary state numbers (e.g. 00, 01, 10, 11).</li> <li>Record types:</li> <li>Define multiple signals into one type.</li> <li>Natural coding style for asynchronous resets.</li> <li>Easily reverse bit order of a word.</li> <li>Logical statement (like case and if/then) endings are clearly marked.</li> <li>Cons :</li> <li>Extremely verbose coding:</li> <li>VHDL modules must be defined by a prototype and declared before they're used, causing you to change code in at least 3 places if you want to make a change to the interface.</li> <li>The use of the keyword "downto" in every bit vector definition is tedious.</li> <li>Sensitivity lists: Missing a single signal in the sensitivity list can cause catastrophic differences between simulation and synthesis.</li> <li>Each process must have a sensitivity list that may sometimes be very long.</li> <li>Type conversions:</li> <li>Signal types that are clearly related (e.g. std_logic and std_logic_vector) cannot be simply used together and must be converted to another type.</li> </ul> |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| iii) | What do you mean by event based and cycle based simulator ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4M       |

|      | <ul> <li>Cycle-based simulators work best with synchronous design but give less timing accuracy with asynchronous design.</li> <li>Signals are treated as variables. Functions such as AND, OR etc. are directly converted to program statements.</li> <li>Signal level functions such as memory blocks, adders, multipliers etc. are modeled as</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2M<br>2M |

| (    | <ul> <li>For every input vector, the code is repeatedly executed until all variables have attained steady value.</li> <li>Compiled code simulator is efficient when used for high-level design verification. Inefficiency is incurred by the evaluation of the design when only few inputs are changing.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| y) List any four Features of Spartan 3 series FPGA.                                                                        | <b>4M</b> |

|----------------------------------------------------------------------------------------------------------------------------|-----------|

| Ans: <u>Features</u> :                                                                                                     | (1M-      |

| • Low-cost, high-performance logic solution for high-volume, consumer-oriented                                             | Any Four  |

| applications                                                                                                               | Features) |

| • Densities up to 74,880 logic cells                                                                                       |           |

| SelectIO interface signaling • Up to 633 I/O pins                                                                          |           |

| • 622+ Mb/s data transfer rate per I/O                                                                                     |           |

| • 18 single-ended signal standards                                                                                         |           |

| • 8 differential I/O standards including LVDS, RSDS                                                                        |           |

| Termination by Digitally Controlled Impedance                                                                              |           |

| • Signal swing ranging from 1.14V to 3.465V                                                                                |           |

| • Double Data Rate (DDR) support                                                                                           |           |

| • DDR, DDR2 SDRAM support up to 333 Mb/s                                                                                   |           |

| <ul> <li>Logic resources • Abundant logic cells with shift register capability</li> <li>Wide, fast multiplexers</li> </ul> |           |

| Fast look-ahead carry logic                                                                                                |           |

| Dedicated 18 x 18 multipliers                                                                                              |           |

| • JTAG logic compatible with IEEE 1149.1/1532                                                                              |           |

| Select RAM hierarchical memory                                                                                             |           |

| • Up to 1,872 Kbits of total block RAM                                                                                     |           |

| • Up to 520 Kbits of total distributed RAM                                                                                 |           |

| Digital Clock Manager (up to four DCMs)                                                                                    |           |

| Clock skew elimination                                                                                                     |           |

| Frequency synthesis                                                                                                        |           |

| High resolution phase shifting                                                                                             |           |

| Eight global clock lines and abundant routing                                                                              |           |

| B) Attempt any ONE :                                                                                                       | 6M        |

| Describe the twin tub process for CMOS fabrication.                                                                        | 6M        |

| Ans: Twin Tub Process:                                                                                                     |           |

| Diagram :                                                                                                                  | 3M        |

| , Vin                                                                                                                      |           |

|                                                                                                                            |           |

| Vdd <                                                                                                                      |           |

| $ \begin{array}{                                    $                                                                      |           |

|                                                                                                                            |           |

| N Tub P tub                                                                                                                |           |

|                                                                                                                            |           |

| P-substrate                                                                                                                |           |

| r-substrate                                                                                                                |           |

| r-substrate                                                                                                                |           |

| r-substrate                                                                                                                |           |

|                                                                                                                            |           |

| N Substrate                                                                                                                |           |

|                                                                                                                            |           |

|             | Explanation :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|             | <ul> <li>The process is carried out on N type silicon substrate with lower doping or higher resistivity, so that the lesser current flows through the substrate. On this, the N+ Si substrate is grown further i.e epitaxial layer of required thickness is grown.</li> <li>SiO2 layer is grown all over the surface, and the areas of P well and N well are defined. P well is diffused by masking N well area and N well is diffused by masking P well area.</li> <li>A thin layer of SiO2 thinox is deposited all over the surface. Using masking and etching process unrequired thinox is removed. The thinox is required only on gate areas of both the transistors.</li> <li>The polysilicon is deposited all over the surface and using a mask it is removed from areas other the gate area.</li> <li>Then the P well is covered with a photoresist mask and P+ diffusion is carried out to form the source and drain of PMOS transistor.</li> <li>Now the N well is covered with a photoresist mask and N+ diffusion is carried out to form the source and drain of NMOS transistor.</li> <li>The thick layer of SiO2 is grown all over the surface for isolation. This SiO2 layer is etched off to expose all the terminals.</li> </ul> | 3M                                                                                |

|             | with source, drain and gate terminals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                   |

| ii)<br>Ans: | Write the VHDL program to implement 4 bit adder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6M                                                                                |

|             | <pre>library IEEE;<br/>use IEEE.STD_LOGIC_1164.ALL;<br/>use IEEE.STD_LOGIC_ARITH.ALL;<br/>use IEEE.STD_LOGIC_UNSIGNED.ALL;<br/>entity adder is<br/>Port ( a : in std_logic_vector(3 downto 0);<br/>b : in std_logic_vector(3 downto 0);<br/>c : out std_logic;<br/>cin : in std_logic;<br/>cin : in std_logic);<br/>end adder;<br/>architecture behavior of adder is<br/>begin<br/>process(a,b,cin)<br/>variable u:std_logic;<br/>begin<br/>u:=cin;<br/>for i in 0 to 3 loop<br/>s(i)&lt;=a(i) xor b(i) xor u;<br/>u:=(a(i) and b(i))or(b(i) and u) or(u and a(i));</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (1M -<br>Package<br>Declaration)<br>(1M –<br>Entity)<br>(4M-<br>Architectur<br>e) |

|             | <pre>end loop;<br/>c&lt;=u;<br/>end process;<br/>end behavior;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                   |

| 2 |            | Attempt any FOUR :                                                                                               | 16-Total<br>Marks                                                                   |

|---|------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|   | a)<br>Ans: | Design a sequence detector '10' using D-FF. If the sequence is valid, it gives the output $z = '1'$ else 'z' =0. | 4M(1M-<br>Excitation<br>Table)(1M-k map)(1M-<br>Implementa<br>tion)(1M-<br>Diagram) |

|   | b)<br>Ans: | Realize the equation y = (u + v) (w + x) using CMOS logic.                                                       | 4M                                                                                  |

|            |                                                                                                                                                                                                                                                                                                                                                                             | <b>4</b> M |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | y = (u+v) (w+2) using cross Loge                                                                                                                                                                                                                                                                                                                                            |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            | $\frac{(u+v)}{(u+v)} + (u+v)$                                                                                                                                                                                                                                                                                                                                               |            |

|            | $=(\overline{u},\overline{\vartheta}) + (\overline{\omega},\overline{z})$                                                                                                                                                                                                                                                                                                   |            |

|            | 100                                                                                                                                                                                                                                                                                                                                                                         |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            | <sup>u</sup> −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−                                                                                                                                                                                                                                                                                                                           |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            | v _olk ~                                                                                                                                                                                                                                                                                                                                                                    |            |

|            | y= (u+v) (w+v)                                                                                                                                                                                                                                                                                                                                                              |            |

|            | I Land                                                                                                                                                                                                                                                                                                                                                                      |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            | $w = \int z$                                                                                                                                                                                                                                                                                                                                                                |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            | Z                                                                                                                                                                                                                                                                                                                                                                           |            |

|            | GND                                                                                                                                                                                                                                                                                                                                                                         |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

| c)         | What do you mean by enumerated data types ? Give the suitable example.                                                                                                                                                                                                                                                                                                      | <b>4M</b>  |

| Ans:       | Enumerated:                                                                                                                                                                                                                                                                                                                                                                 | 2M         |

|            | Defines the set of user defined values consisting of identifiers and character literals                                                                                                                                                                                                                                                                                     |            |

|            | <b>Example :</b><br>type opcode is (load,store,add); opcode is enumerated type and supports load,store,add                                                                                                                                                                                                                                                                  | 2M         |

|            | type mul is ('U', '0', '1', 'Z'); set of ordered values U', '0', '1', 'Z'                                                                                                                                                                                                                                                                                                   |            |

| <b>d</b> ) | What do you mean by test bench ? State its applications.                                                                                                                                                                                                                                                                                                                    | 4M         |

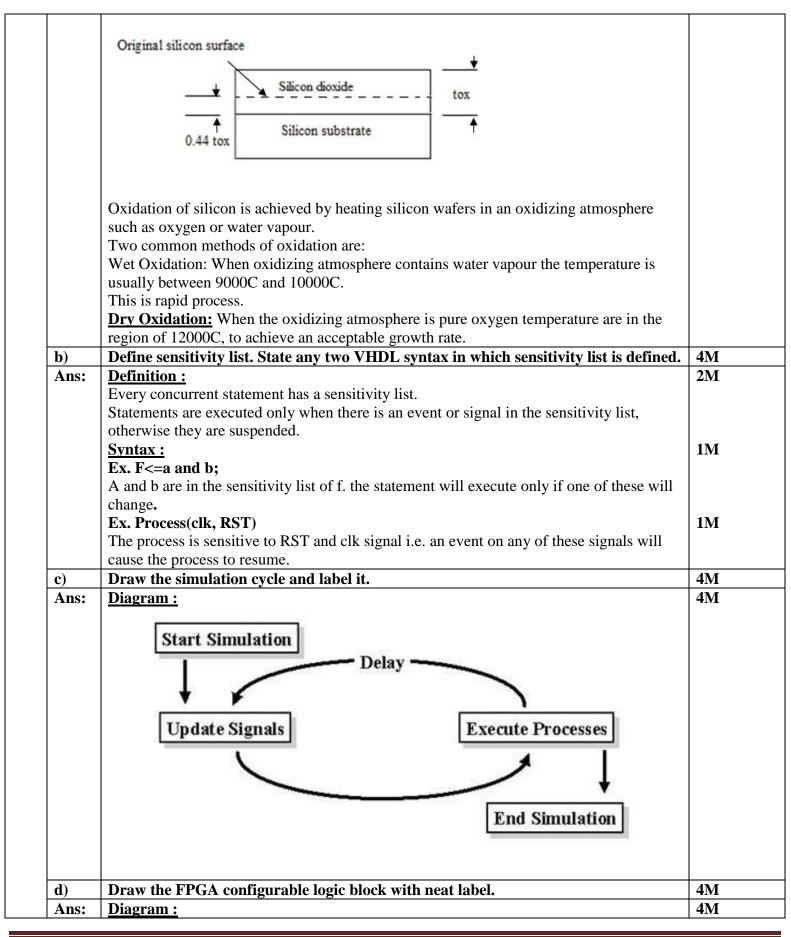

| Ans:       | Definition :                                                                                                                                                                                                                                                                                                                                                                | 2M         |

| 111.5.     | A test bench is HDL code that allows you to provide a documented, repeatable set of                                                                                                                                                                                                                                                                                         |            |

|            | stimuli that is portable across different simulators. A test bench can be as simple as a file                                                                                                                                                                                                                                                                               |            |

|            | with clock and input data or a more complicated file that includes error checking, file                                                                                                                                                                                                                                                                                     |            |

|            | input and output, and conditional testing. It encapsulates the stimulus driver, known good                                                                                                                                                                                                                                                                                  |            |

|            | results, and DUT and contains internal signals to make the proper connections. The stimulus driver drives the input into DUT which responds and produces results. Finally a                                                                                                                                                                                                 |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            |                                                                                                                                                                                                                                                                                                                                                                             |            |

|            | compare function within the test bench compares the result from the DUT against those known good results and reports any errors.                                                                                                                                                                                                                                            |            |

|            | compare function within the test bench compares the result from the DUT against those known good results and reports any errors.<br><u>Applications :</u>                                                                                                                                                                                                                   |            |

|            | <ul> <li>compare function within the test bench compares the result from the DUT against those known good results and reports any errors.</li> <li><u>Applications :</u></li> <li>A test bench or testing workbench is an (often virtual) environment used</li> </ul>                                                                                                       | 2M         |

|            | <ul> <li>compare function within the test bench compares the result from the DUT against those known good results and reports any errors.</li> <li><u>Applications</u>:</li> <li>A test bench or testing workbench is an (often virtual) environment used to verify the correctness or soundness of a design or model, for example, that of a</li> </ul>                    | 2M         |

|            | <ul> <li>compare function within the test bench compares the result from the DUT against those known good results and reports any errors.</li> <li><u>Applications :</u></li> <li>A test bench or testing workbench is an (often virtual) environment used to verify the correctness or soundness of a design or model, for example, that of a software product.</li> </ul> | 2M         |

|            | <ul> <li>compare function within the test bench compares the result from the DUT against those known good results and reports any errors.</li> <li><u>Applications</u>:</li> <li>A test bench or testing workbench is an (often virtual) environment used to verify the correctness or soundness of a design or model, for example, that of a</li> </ul>                    | 2M         |

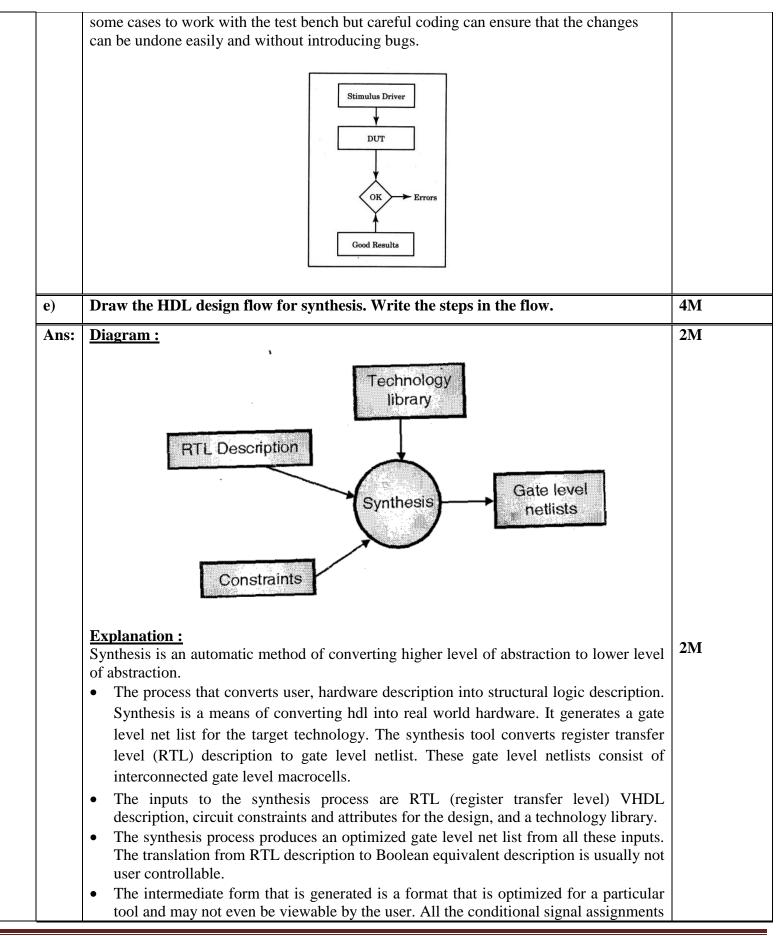

|      |            | <ul> <li>and selected signal assignment statements are converted to their boolean equivalent in this intermediate form. The optimization process takes an un optimized Boolean description and converts it to an optimized Boolean description. For this it uses number of algorithm and rules. This process aims to improve structure of Boolean equations by applying rules of boolean algebra. This removes the redundant logic and reduces the area requirement.</li> <li><u>OR</u></li> <li><u>Simple steps</u>:</li> <li>1. Describe your design with HDL</li> <li>2. Perform RTL simulation</li> <li>3. Synthesizing your design</li> <li>4. Create Xilinx Netlist Files (XNF/EDIF etc)</li> <li>5. Perform Functional Simulation</li> <li>6. Floor planning of design (optional)</li> <li>7. Placing and routing</li> <li>9. Durforms a timing aimselfting (seet hereart)</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|      | <b>f</b> ) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | form a timing simulation (post lay<br>are FPGA and CPLD (any four)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                       | 4M                          |

| •    | Ans:       | <b>r</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ·····                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

|      |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>FPGA</li> <li>It is field programmable gate arrays.</li> <li>Capacity is defined in terms of numb<br/>gates available.</li> <li>FPGA consumes less power than CP</li> <li>Numbers of input and output pin<br/>FPGA are less than CPLD.</li> <li>FPGA is suitable for designs with<br/>number of simple blocks with<br/>numbers of inputs.</li> <li>FPGA based designs require more to<br/>space and layout complexity is more.</li> <li>It is difficult to predict the sperformance of design.</li> <li>FPGA are available in wide de<br/>range.</li> </ul> | macro-cells available.         LD       CPLD consumes more power than FPGA devices.         is on       Numbers of input and output pins on CPLD are high.         large       CPLD are ideal for complex blocks with large number of inputs.         poard       CPLD based designs need less board space and less board layout complexity.         speed       It is easier to predict speed performance of design. | (1M-<br>Any Four<br>Points) |

| Q. 3 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ot any FOUR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16M                         |

|      | a)         | What                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s metastability ? Give the exam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ple.                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>4M</b>                   |

|      | Ans:       | In digi<br>resultir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | g output goes to an indeterminate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ous signals combine in such a way that their<br>e state or unpredictable state. This state is known<br>able state the output settles either 0 or 1. This                                                                                                                                                                                                                                                              | 2M                          |

|      | <b>Example:</b><br>A simple<br>when both<br>(R=0 and S<br>simultaneo<br>flip-flop w<br>other false<br>transitions | Set and Reset inputs are true (R=<br>S=0) at about the same time. Both<br>ous Set and Reset inputs. After b<br>ill (eventually) end up in one of t<br>. The final state will depend on w     | can be found in an SR NOR latch,<br>=1 and S=1) and then both transition to false<br>a outputs Q and Q are initially held at 0 by the<br>oth Set and Reset inputs change to false, the<br>two stable states, one of Q and Q true and the<br>hich of R or S returns to zero first, but if both<br>resulting metastability, with intermediate or<br>long to resolve to a stable state. | 2M            |

|------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| b)   | Compare                                                                                                           | BJT and CMOS (any four).                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                      | <b>4</b> M    |

| Ans: | Sr.No.                                                                                                            | CMOS Technology                                                                                                                                                                              | Bipolar Technology                                                                                                                                                                                                                                                                                                                                                                   | (1 <b>M</b> - |

|      | 1.                                                                                                                | Low static power dissipation                                                                                                                                                                 | High power dissipation                                                                                                                                                                                                                                                                                                                                                               | Any four      |

|      | 2.                                                                                                                | High input impedance                                                                                                                                                                         | Low input impedance                                                                                                                                                                                                                                                                                                                                                                  | point)        |

|      | 3.                                                                                                                | High packing density                                                                                                                                                                         | Low packing density                                                                                                                                                                                                                                                                                                                                                                  |               |

|      | 4.                                                                                                                | High delay sensitive to load                                                                                                                                                                 | Low delay sensitive to load                                                                                                                                                                                                                                                                                                                                                          |               |

|      | <u>5.</u><br>6.                                                                                                   | Low output drive current<br>Bidirectional capability                                                                                                                                         | High output drive current<br>Essentially unidirectional                                                                                                                                                                                                                                                                                                                              |               |

|      | 0.<br>7.                                                                                                          | It is an ideal switching device.                                                                                                                                                             | It is not an ideal switching device.                                                                                                                                                                                                                                                                                                                                                 |               |

|      | 8.                                                                                                                | Voltage driven                                                                                                                                                                               | Current driven                                                                                                                                                                                                                                                                                                                                                                       |               |

|      | 9.                                                                                                                | High power application                                                                                                                                                                       | Low power application                                                                                                                                                                                                                                                                                                                                                                |               |

|      | 10.                                                                                                               | Unipolar device                                                                                                                                                                              | Bipolar Device                                                                                                                                                                                                                                                                                                                                                                       |               |

|      | 11.                                                                                                               | High current gain                                                                                                                                                                            | Low current gain                                                                                                                                                                                                                                                                                                                                                                     |               |

|      | 12.                                                                                                               | It has less fan out                                                                                                                                                                          | It has more fan out.                                                                                                                                                                                                                                                                                                                                                                 |               |

| c)   | Define 1.1                                                                                                        | Entity 2.Architecture in VHDL.                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                      | <b>4</b> M    |

| Ans: | basic build<br>The entity<br>ports, the c<br>One entity                                                           | ing block in the design. A design<br>describes the interface to the ou<br>lirection of the ports, and the type<br>can be associated with much arch                                           | -                                                                                                                                                                                                                                                                                                                                                                                    | 2M            |

|      | describes t<br>inputs and<br>Architectur                                                                          | that are declared have an archite<br>the behavior, functionality, inter-<br>outputs. Architecture contains on<br>re is always related to an entity ar<br>of the architecture may contain de- | cture associated with it. Architecture<br>connections or relationship between<br>ly concurrent statement.<br>ad describes the behavior of that entity.<br>claration of types, signals, constants,                                                                                                                                                                                    | 2M            |

| d)   | What the                                                                                                          | different measure should be tak                                                                                                                                                              | ten to write the efficient code?                                                                                                                                                                                                                                                                                                                                                     | <b>4</b> M    |

| Ans: | The style of can make                                                                                             | • •                                                                                                                                                                                          | nportant. Effective VHDL coding techniques igns that meet tough synthesis targets and                                                                                                                                                                                                                                                                                                | 4M            |

|   |                                                                                                                                              | • It must viald avaaatad ragulta                                                                                                                                         | 1         |  |  |  |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

|   | <ul> <li>It must yield expected results.</li> <li>It must follow VHDL language rules.</li> </ul>                                             |                                                                                                                                                                          |           |  |  |  |  |

|   | <ul> <li>It must follow VHDL language rules.</li> <li>It should have common look to enhance familiarity between different models.</li> </ul> |                                                                                                                                                                          |           |  |  |  |  |

|   |                                                                                                                                              | • It should have common look to enhance familiarity between different models.                                                                                            |           |  |  |  |  |

|   |                                                                                                                                              | • Out dated VHDL should be avoided.                                                                                                                                      |           |  |  |  |  |

|   |                                                                                                                                              | • The common functions should be lumped in common packages, partitions or                                                                                                |           |  |  |  |  |

|   |                                                                                                                                              | architectures.                                                                                                                                                           |           |  |  |  |  |

|   |                                                                                                                                              | • Behavioral and structural coding should be kept separate to reduce the debugging                                                                                       |           |  |  |  |  |

|   |                                                                                                                                              | time                                                                                                                                                                     |           |  |  |  |  |

|   |                                                                                                                                              | • Use one line for each signal in declarations instantiations and mappings which                                                                                         |           |  |  |  |  |

|   |                                                                                                                                              | maintains clarity, more readable and understandable code.                                                                                                                |           |  |  |  |  |

|   |                                                                                                                                              | To avoid accidental mixing of signal use named Association                                                                                                               |           |  |  |  |  |