(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

\_\_\_\_\_\_

#### **Important Instructions to examiners:**

- 1) The answers should be examined by keywords and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance. (Not applicable for subject English and Communication Skills.)

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

Q. **Question & its Answer** Remark Total No. Marks 01A) 12 **Attempt Any THREE** Compare open loop and close loop control system 04 **i**) Ans No. **Open Loop Control System Close Loop Control System** It is simple and economical It is complex and costlier 1 1 mark 2 It is not easy to construct, as it It is easier to construct, as it for each requires less number requires more number of point components components Any 3 It consumes less power It consumes more power 04 4 It is more stable It is less stable points) 5 It does not require feedback It requires feedback path element element It has poor accuracy It has better accuracy 6 It gives automatic correction It does not give automatic for external disturbances correction for external disturbances 8 It is more sensitive to noise It is less sensitive to noise It is dependent on operating is not dependent on condition operating conditions Its operation is degraded if operation 10 is not non linearity is present independent on conditions It has slow response It has fast response 11

**WINTER - 15 EXAMINATION** Subject Code: 17536 **Model Answer**

|      | 12                                                                                                                                                                                                                                                                                                 | It has high bandwidth                                                                                                                                                                                   | It has low bandwidth                                                            |        |                                                            |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------|------------------------------------------------------------|-----|

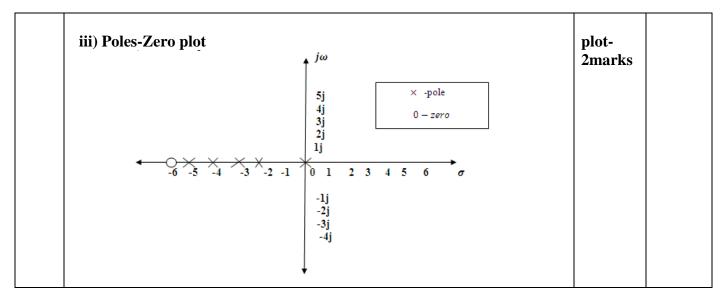

| ii)  | Doffic                                                                                                                                                                                                                                                                                             | or a)Dalas h) Zanas a)Ondan af                                                                                                                                                                          | avatom d) Chamastanistic acros                                                  | otion  |                                                            | 04  |

| Ans  |                                                                                                                                                                                                                                                                                                    | e: a)Poles b) Zeros c)Order of fer function of standard control sy                                                                                                                                      |                                                                                 | auon   |                                                            | U4  |

|      |                                                                                                                                                                                                                                                                                                    | $G(s) = \frac{K'(S-Z)}{S^{j}(S-P)}$                                                                                                                                                                     | ,                                                                               |        |                                                            |     |

|      | a)                                                                                                                                                                                                                                                                                                 | <b>Poles:</b> The poles of the system polynomial of transfer function $P_1, P_2,$ Are poles of the system                                                                                               | . i.e. in above transfer function                                               |        | 1 mark                                                     |     |

|      | <b>b) Zeros:</b> The zeros of the system are roots of the numerator polynomial of transfer function. i.e. in above transfer function G(s) $Z_1, Z_2, \ldots$ Are zeros of the system.                                                                                                              |                                                                                                                                                                                                         |                                                                                 |        |                                                            |     |

|      | <ul> <li>c) Order of system: It is highest power of 'S' at denominator of closed loop T.F.</li> <li>In case of electrical circuit network number of energy storing device also give order of system.</li> </ul>                                                                                    |                                                                                                                                                                                                         |                                                                                 |        |                                                            |     |

|      | <b>d) Characteristics Equation:</b> The characteristics equation of the control system can be obtained by simplifying the denominator of the transfer function. In above transfer function G(s), the characteristics equation can be obtained from by salving equation $S^{j}(S-P^{1})(S-P^{2})=0$ |                                                                                                                                                                                                         |                                                                                 |        | 1 Mark                                                     |     |

| iii) | State a                                                                                                                                                                                                                                                                                            | ndvantages of PLC                                                                                                                                                                                       |                                                                                 |        |                                                            | 04  |

|      | •                                                                                                                                                                                                                                                                                                  | human Higher productivity Superior quality of end products Efficient uses of energy and raw Eliminate the high costs associ systems Improved safety in working con Easily programmed and have language. | material ated with inflexible, relay-contrditions. an easily understood program | rolled | 1 mark<br>for each<br>advanta<br>ge ( Any<br>04<br>points) | 0.4 |

| iv)  | Draw<br>blocks                                                                                                                                                                                                                                                                                     | block diagram of Process Con                                                                                                                                                                            | ntrol System. State functions                                                   | of its |                                                            | 04  |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

Ans R(t) Amplifier Actuator Process or plant Diagra m – 2 Marks Sensor Automatic controller **Explanation** - Process control system consists of process or plant ,sensor, error detector, automatic Controller, actuator or control element. 1) Process or plant- process means some manufacturing sequence. It has **Explana** one variable or multivariable output. Plant or process is an important element tion of process control system in which variable of process is to be controlled. 2 Marks 2) Sensor/measuring elements – It is the device that converts the output variable into another suitable variable which can acceptable by error detector Sensor is present in f/b path of close loop system. 3) Error detector – Error detector is summing point whose output is an error signal i.e. e(t) = r(t) - b(t) to controller for comparison & for the corrective action. Error detector compares between actual signal & reference i/p i.e. set point. 4) Automatic controller- Controller detects the actuating error signal, which is usually at a very low power level, and amplifies it to a sufficiently high level .i.e. means automatic controller comprises an error detector and amplifier. 5) Actuator or control element – Actuator is nothing but pneumatic motor or valve, a hydraulic motor or an electric motor, which produces an input to the plant according to the control signal getting from controller.

OR

(Autonomous)

#### (ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

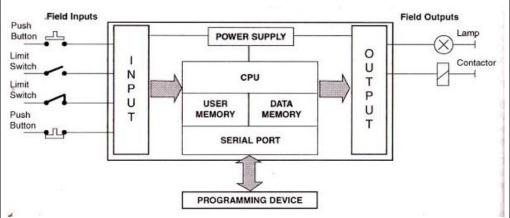

Control element Process Controller Summing point Measurement **Explanation:** The block diagram of process control system consists of the following blocks:-1) Measuring element: It measures or senses the actual value of controlled variable "c" and converts it into proportional feedback variable b. 2) Error detector: It receives two inputs: set point "r" and controlled variable "p". The output of the error detector is given by e= r-b. "e" is applied to the controller. 3) Controller: It generates the correct signal which is then applied to the final control element. Controller output is denoted by "p". 4) Final control element: It accepts the input from the controller which is then transformed into some proportional action performed by the process. Output of control element is denoted by "u". 5) **Process:** Output of control element is given to the process which changes the process variable. Output of this block is denoted by "u". Q1B Attempt Any ONE. 06 i) Draw block diagram of PLC. Describe working of different parts of 06 PLC. A simplified block diagram of a PLC shown in Fig. It has three major units. Ans. I/O (Input/Output) Modules. CPU (Central Processing Units). Programmer/Monitor.

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

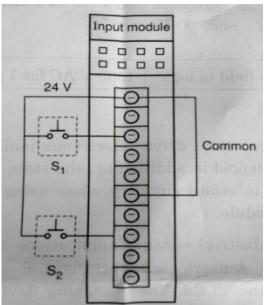

#### 1) I/O Section:-

The I/O section establish the interfacing between physical devices in the real world outside the PLC and the digital arena inside the PLC. The input module has bank of terminals for physically connecting input devices, like push buttons, limit switches etc. to a PLC. the role of an input module is to translate signals from input devices into a form that the PLC's CPU can understand. The Output module also has bank of terminals that physically connect output devices like solenoids, motor starters, indicating lamps etc. to a PLC. The role of an output module is to translate signals from the PLC's CPU into a form that the output device can use.

The tasks of the I/O section can be classified as:

- Conditioning

- Isolation

- Termination

- Indication

An electronic system for connecting I/O modules to remotely located I/O devices can be added if needed. The actual operating process under PLC Control can be thousands of feet from the CPU and its I/O modules.

Block

Diagra

m –

2 Marks

#### **Block diagram of PLC**

#### 2) CPU Section:-

The Central Processing Unit, the brain of the system is the control portion of the PLC. It has three Subparts.

- Memory System

- Processor

- Power Supply

**Memory System:-** The memory is the area of the CPU in which data and information is stored and retrieved. The total memory area can be subdivided into the following four Sections.

Explana tion – 4 Marks

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

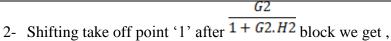

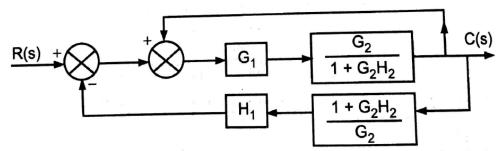

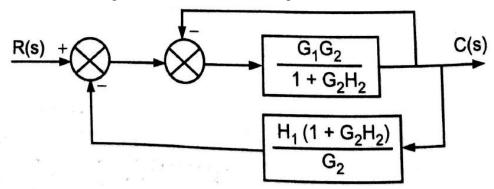

I/O Image Memory Data Memory **User Memory Executive Memory Processor:-** The processor, the heart of CPU is the computerized part of the CPU in the form of Microprocessor / Micro controller chip. It supervises all operation in the system and performs all tasks necessary to fulfill the PLC function. **Power Supply:-** The power supply provides power to memory system, processor and I/O Modules. It converts the higher level AC line Voltage to various operational DC values. 3) Programmer/Monitor:-The Programmer/Monitor (PM) is a device used to communicate with the circuits of the PLC. The programming unit allows the engineer/technicians to enter the edit the program to be executed. With the help of proprietary software, it allows programmer to write, view and edit the program and download it into the PLC. It also allows user to monitor the PLC as it is running the program. With this monitoring systems, such things as internal coils, registers, timers and other items not visible externally can be monitored to determine proper operation. Also, internal register data can be altered, if required. ii) Derive transfer function of block diagram shown in fig. using block 06 diagram reduction rules. C(s)R(s)Ans. Combining block G2 & H2, we get, 6 marks (Consid C(s) er  $+ G_2H_2$ stepwise markin combini ng blocks,s

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

\_\_\_\_\_

3- Combining two cascaded blocks, we get

4- Salving unit negative feedback loop i.e. H(s) = 1

$$\frac{\frac{G_1G_2}{1 + G_2H_2}}{1 + \frac{G_1G_2}{1 + G_2H_2}} = \frac{G_1G_2}{1 + G_2H_2} \times \frac{1 + G_2H_2}{1 + G_1G_2 + G_2H_2}$$

$$\frac{G_1G_2}{1 + G_2G_2}$$

$$G_1G_2$$

$$= \frac{G_1G_2}{1 + G_1G_2 + G_2H_2}$$

5- After eliminating unity feedback loop we get,

hifting take of points, combini ng cascade block, feedbac k gain, final answer etc.)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536

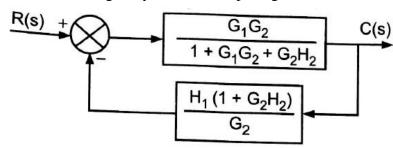

|     | 6- Salving two blocks in parallel we get,                                                                                                                                                                                                              |                          |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----|

|     | where, $G(s) = \frac{1 + G_1G_2}{1 + G_1G_2 + G_2H_2}$                                                                                                                                                                                                 |                          |    |

|     | $H(s) = \frac{H_1 (1 + G_2 H_2)}{G_2}$                                                                                                                                                                                                                 |                          |    |

|     | $\frac{G(s)}{1 + G(s) \cdot H(s)} = \frac{\frac{G_1 G_2}{1 + G_1 G_2 + G_2 H_2}}{1 + \left(\frac{G_1 G_2}{1 + G_1 G_2 + G_2 H_2}\right) \cdot \left(\frac{H_1 + H_1 H_2 G_2}{G_2}\right)}$                                                             |                          |    |

|     | $= \frac{\frac{G_1G_2}{1 + G_1G_2 + G_2H_2}}{\frac{1 + G_1G_2 + G_2H_2 + G_1H_1 + G_1G_2H_1H_2}{(1 + G_1G_2 + G_2H_2)}}$                                                                                                                               |                          |    |

|     | $= \frac{G_1G_2}{1 + G_1G_2 + G_2H_2 + G_1H_1 + G_1G_2H_1 H_2}$ 7- Thus, combining two parallel blocks we get,                                                                                                                                         |                          |    |

|     | R(s) $ \frac{G_1G_2}{1 + G_1G_2 + G_2H_2 + G_1H_1 + G_1G_2H_1H_2}                                    $                                                                                                                                                 |                          |    |

| Q2  | Attempt any TWO                                                                                                                                                                                                                                        |                          | 16 |

| a)  | A system is given by differential equation $\frac{d^2y}{dx} + 4 \cdot \frac{dy}{dx} + 8 \cdot y = 8 \cdot x$ . Where y is output and x is input. Determine time domain specification. i) Rise Time ii) Peak Time iii) Settling Time iv) Peak overshoot |                          | 08 |

| Ans | mysetting Time IV) I can overshoot                                                                                                                                                                                                                     |                          |    |

|     | Taking Laplace for zero initial conditions, we get $s^{2}Y(s) + 4sY(s) + 8Y(s) = 8X(s)$ $(s^{2} + 4s + 8) Y(s) = 8X(s)$                                                                                                                                |                          |    |

|     | $\frac{Y(s)}{X(s)} = \frac{8}{s^2 + 4s + 8}$                                                                                                                                                                                                           |                          |    |

|     | Comparing with standard form, we get                                                                                                                                                                                                                   |                          |    |

|     | $\omega_{\rm h}^2 = 8$ $\therefore \omega_{\rm h} = \sqrt{8} = 2.828 \text{ rad/s}.$                                                                                                                                                                   |                          |    |

|     | $2\xi\omega_{n} = 4$                                                                                                                                                                                                                                   | Equatio<br>n – 1<br>Mark |    |

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536

|            |                                                                                                                                | , ,              |    |

|------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|----|

|            | $Wd = Wn\sqrt{1-\xi^2} = 2.828\sqrt{1-0.707^2} = 2 \text{ rad/s}$                                                              | Wn-1             |    |

|            | (ii) Rise time, $t_r = \frac{\pi - \beta}{\omega_d} \text{ where } \beta = \frac{\sqrt{1 - \xi^2}}{\xi} = 0.7853$              | M                |    |

|            | $T_r = \frac{3.14 - 0.7853}{2} = 1.178 \text{ sec.}$                                                                           | ζ–1Μ             |    |

|            | (iii) Peak time, $t_p = \frac{\pi}{\omega_t} = \frac{3.14}{2} = 1.5707 \text{ sec.}$                                           | Wd-1M<br>Tr - 1M |    |

|            |                                                                                                                                |                  |    |

|            | (iv) Peak overshoot time, $\%M_p = \frac{4}{\xi \omega_h} = 100 \times e^{\sqrt{1-\xi^2}}$                                     |                  |    |

|            | or $\%M_p = 100 \times e^{\frac{-0.707 \times 3.14}{\sqrt{1 - (0.707)^2}}}$                                                    | Tp-1M            |    |

|            | = 4.321%                                                                                                                       | Mp-1M            |    |

|            | 4 4                                                                                                                            |                  |    |

|            | (v) Settling time, $t_s = \frac{4}{\xi \omega_n} = \frac{4}{\left(\frac{1}{\omega^2}\right) \times \sqrt{8}} = 2 \text{ sec.}$ | Ts-1M            |    |

| <b>b</b> ) | For unity feedback system having open loop transfer function                                                                   |                  | 08 |

|            | $G(s) = \frac{K(S+2)}{S(S^2 + 7S^2 + 12S)}$                                                                                    |                  |    |

|            | Find i) Type of System ii) All error coefficients iii) Steady state error for input $r(t) = R/2.t^2$                           |                  |    |

| Ans.       | 1) As H(s) = 1, so G(s).H(s) = $\frac{K(S+2)}{S^2(S^2+7S+12)} = \frac{K(S+2)}{S^2(S+4)(S+3)}$                                  |                  |    |

|            | Consider the first term in the $S^2$ denominator. This gives (n=2) poles at origin of s-plane. <b>So it is Type 2 system</b>   |                  |    |

|            | 2) Positional error coefficient (K <sub>p</sub> ) is given by,                                                                 |                  |    |

|            | $K_{p} = \lim_{s \to 0} G(s).H(s)$                                                                                             |                  |    |

|            | $K_p = \lim_{s \to 0} \frac{K(s+2)}{s^2(s+4)(s+3)}$                                                                            |                  |    |

|            | $K_p = \infty$                                                                                                                 |                  |    |

|            | 3) Velocity error coefficient $(K_v)$ is given by,                                                                             |                  |    |

|            | L                                                                                                                              | 1                |    |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536

#### **Model Answer**

$K_v = \lim_{s \to 0} s. G(s). H(s) = \overline{\lim_{s \to 0} \frac{K(s+2)}{s(s+4)(s+3)}}$  $K_n = \infty$ 4) Acceleration error coefficient (K<sub>a</sub>) is given by,  $K_a = \lim_{s \to 0} S^2 \cdot G(s) \cdot H(s) = \lim_{s \to 0} \frac{K(s+2)}{(s+4)(s+3)}$  $K\alpha = \frac{K}{6}$ 5) Steady State Error is given as,  $ess = \lim_{s \to 0} \frac{s \cdot X(s)}{1 + G(s) \cdot H(s)}$ As  $x(t) = R/2.t^2$ , so input is parabolic function. For parabolic function steady state error is given as, Ess = R / Ka =  $\frac{6.R}{V}$ OR  $X(s) = R/S^3$ , we get  $ess = \lim_{s \to 0} \frac{s \cdot X(s)}{1 + G(s) \cdot H(s)} = \lim_{s \to 0} \frac{S \cdot \frac{R}{s^2}}{1 + \frac{K(S+2)}{s^2(S+4)(S+3)}}$  $ess = \lim_{s \to 0} \frac{R(S+4)(S+3)}{S^2(S+4)(S+3) + K(S+2)} = \frac{6.R}{K}$ Draw ladder diagram for two motor system with following condition c) 08 i) Start switch starts motor 1 ii) 10 seconds later motor 2 starts iii) Stop switch stops motor 1 iv) 15 seconds later motor 2 stops i) Start switch starts motor 1 Ans. 01 Mark

#### **WINTER - 15 EXAMINATION**

| 1) Start push button, start motor M <sub>1</sub>                                                     |            |          |

|------------------------------------------------------------------------------------------------------|------------|----------|

| 1   1   (S)   I1 is push button, Q1 is output relay for motor M <sub>1</sub>                         | 03<br>Mark |          |

| ii) 10 seconds later motor 2 starts                                                                  |            |          |

| After setting Q1, T1 timer will get on after 10 seconds. After T1 ON Q2 will set.                    |            |          |

| iii) Stop switch stops motor 1                                                                       | 1 Mark     |          |

| I2 is push button, After pushing I2, Q1 will reset                                                   | 03         |          |

| iv) 15 seconds later motor 2 stops                                                                   | Mark       |          |

| At Q1 reset & Q2 Set state, T2 timer will get on after 15 seconds. Q2 will reset when T2 will be ON. |            |          |

| Q2   Q1   T2   T2   T2   T2   T2   T2   T2   T                                                       |            |          |

| Note: Any relevant ladder logic may considered.                                                      |            | 17       |

| 2. 3 Attempt any FOUR of the following Derive transfer function of RC Network.                       |            | 16<br>04 |

| ns.                                                                                                  |            |          |

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536

|            | R-C circuit  Transfer function of the circuit is defined as, $L \frac{\{Output\}}{\{Input\}} = \frac{L \{V_o(t)\}}{L \{V_i(t)\}} = \frac{V_o(s)}{V_i(s)}$ From figure apply KVL to input loop we get, $V_i(t) = R_i(t) + \frac{1}{C} \int i(t)dt$ $V_o(t) = \frac{1}{C} \int i(t)dt$ • Neglecting initial conditions, taking Laplace of $V_i(t)$ and $V_o(t)$ we get, $V_i(s) = R \cdot I(s) + \frac{1}{sC} \cdot I(s)$ $V_o(s) = \frac{1}{sC} \cdot I(s)$ $I(s) = sC \cdot V_o(s)$ Substituting value of $I(s)$ in Equation (1.6.9) we get, $V_i(s) = R \cdot sC \cdot V_o(s) + V_o(s)$ $V_i(s) = V_o(s) [1 + sCR]$ $\frac{V_o(s)}{V_i(s)} = \frac{1}{[1 + sCR]}$ Where RC is a time constant • The above system can be represented as shown below, | 2 marks for transfer function  2 marks For Vi(s) and Vo(s) |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----|

| <b>b</b> ) | $Vi(s) \longrightarrow \frac{1}{sCR} \longrightarrow Vo(s)$ Describe the proportional control action w. r. t. eqn and response. State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                            | 04 |

| <b>A</b> : | significance of proportional band.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |    |

| Ans.       | Proportional control action— The output of the controller is proportional to the input error signal. One to one correspondence exists only for errors in this range. Proportional mode can be expressed mathematically by- $p = K_p \; e(t) \; + e_0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Descrip<br>tion- 2<br>Mark,                                |    |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

where, K<sub>p</sub> - proportional gain between error and controller output. e<sub>0</sub> - Controller output with no error. Saturation Respons 100 e-1 Gain G. Mark Controller output (%) 50 Gain G<sub>2</sub> < G (-)0 (+) Error (% Narrow Band Wide Band Fig- Proportional mode controller action **Signific** Proportional Band significance ance-The range of error to cover the 0% to 100% controller output is Mark. called proportional band. Which specifies the percentage error that result in a 100% change in the controller output. Draw block diagram of servo system. State function of its component. c) 04 **Definition:** Ans. Servo system is one type of feedback control system in which control variable is the mechanical load position &its time derivatives like velocity **Block** and acceleration. diagra m-Error voltage Mark, Reference position Difference in Output shaft **Amplifier** angular positions position of shaft Output position (feed back) Fig- standard block diagram of Servo system

**WINTER - 15 EXAMINATION** Subject Code: 17536 **Model Answer**

|      | Fig- DC Servo system  Explanation:  • The standard block diagram of servo system consists of error detector, amplifier, motor as controller, load whose position is to be changed.  • Servo systems is to be divided into two type  a) DC servo systems b) AC servo system  • DC servo system consists of potentiometer as a error detector, DC amplifier, DC motor, DC gear system and the DC load whose position is to be changed.  • In DC servo system potentiometer has two input i.e one is reference input and another is actual load position. Potentiometer finds the error between two positions.  • The errors between two positions is given to DC amplifier which amplify the error.  • Output of DC amplifier is given to DC motor &finally DC motor change the position of DC load. In this way servo system is used to change the load position with help of motor &error detector. | Descrip<br>tion-<br>2Mark. |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----|

| d)   | Define the terms- i. Stable systems ii. Unstable system iii. Critically stable iv. Conditionally stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            | 04 |

| Ans. | 17. Conditionally stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |    |

### **WINTER - 15 EXAMINATION**

|            | <ul> <li>STABLE: A linear time invariant system is said to be stable if following conditions are satisfied:         <ol> <li>When the system is excited by a bounded input, output is also bounded and controllable.</li> <li>In the absence of the input, output must tend to zero irrespective of the initial condition.</li> <li>UNSTABLE: A linear time invariant system is said to be unstable if following conditions are satisfied:</li></ol></li></ul> | 1-Mark<br>each                             |    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----|

| <b>e</b> ) | Draw block diagram of DC input module of PLC. Describe its working.                                                                                                                                                                                                                                                                                                                                                                                            |                                            | 04 |

| Ans.       | Block Diagram-  Noise and Debounce Filter  Noise and Debounce Filter  Noise and Debounce Filter  LED                                                                                                                                                                                                                                                                                                                                                           | 02<br>marks<br>for<br>block<br>diagra<br>m |    |

|            | Fig- DC input module of PLC                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |    |

|            | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |    |

|            | AC Input Signal L2  Power  Input status indicator  Logic  Logic  Logic  Logic  Logic  Logic  Logic                                                                                                                                                                                                                                                                                                                                                             |                                            |    |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

\_\_\_\_\_

| <b>W W</b> 7 | 1  |     |     |

|--------------|----|-----|-----|

| W            | or | ΚIJ | ng- |

#### **Power conversion:**

It consists of rectifier which converts the incoming AC signal to a pulsating dc level, which is passed through filter and other logic in order to deliver a clean and denounced dc signal.

### 02 marks for working

#### **Threshold detector:**

It detects if monitoring signal has reached or exceeded a predetermine d value. A valid ON sate will be between 80- 132V ac. The upper voltage limit for a valid OFF state is below 20V. The voltage between 20V and 80V is called undefined zone.

#### **Isolation:**

It is made up of an optical isolator which separate high voltage from CPU" s low voltage control logic.

#### **Logic section:**

It passes the input signal to the modules input address LED and the CPU.

Fig- wiring of input signal into 24V DC 8 point input

| Q. 4 | Attempt any THREE                                                       |         | 12 |

|------|-------------------------------------------------------------------------|---------|----|

| i)   | State Routh's stability criteria. State its advantages.                 |         | 04 |

| Ans. | Statement-                                                              | Stateme |    |

|      | The necessary & sufficient condition for system to be stable is "All    | nt-02   |    |

|      | the terms in the first column of routh array must have same sign. There | Marks,  |    |

|      | should not be any sign change in the first column of Routh's array".    | ŕ       |    |

|      |                                                                         |         |    |

### **WINTER - 15 EXAMINATION**

|      | If there are any sign changes existing then, (1) System is unstable (2) The number of sign changes equals the number of roots lying in the right half of the S- plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----|

|      | <ol> <li>Advantages-         <ol> <li>Simple method to determine the stability of system, without actually solving characteristics equation of the system.</li> <li>Range of K (variable gain) can be determined.</li> <li>Number of roots of characteristics equation with positive real parts can be given by this method for unstable system.</li> <li>Relative stability, marginally stability can be determined.</li> <li>No time wastage in solving high order determinants like Hurwitz method.</li> <li>Frequency of sustained oscillation can be determined.</li> </ol> </li> </ol>                                                                                                                                             | Advant<br>ages- 02<br>Marks(<br>any 2) |    |

|      | Draw block diagram of PLC power supply. State functions of its components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        | 04 |

| Ans. | AC step down input step down rectifier rectifier network Voltage regulator DC voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Block<br>Diagra<br>m- 02<br>Marks,     |    |

|      | Block diagram of power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |    |

|      | <ul> <li>Description-</li> <li>The power supply of PLC consists of step down transformer which operates with 120V AC input followed by rectifier circuit which converts the AC input to pulsating DC, this signal is filtered with filter circuit. Specific DC voltage level is achieved by regular circuit.</li> <li>Power supply unit provides specific power to different parts of the PLC. In most of the PLC power supply is inbuilt structure or sometime it may separate module, each rack must have its own power supply.</li> <li>PLC power supply converts the AC voltage supply which is usually 115 V AC or 240V AC, into low level DC voltage which is required for different parts of PLC like I/O module, CPU.</li> </ul> | Descrip<br>tion- 02<br>Marks.          |    |

|      | Explain ON/OFF delay timer instruction with diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        | 04 |

| Ans. | Depending on the time delay and operation there are two types of timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |    |

|      | PLC timer- (i) ON delay timer (ii) OFF delay timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |    |

|      | ON delay timer-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 02                                     |    |

|      | • This instruction counts time interval when conditions preceding it in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | marks                                  |    |

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536 <u>Model Answer</u>

\_\_\_\_\_\_

- the rung are true. Produces an output when accumulated reaches the preset value.

- Use Ton instruction to turn an output on or off after the timer has been on for a preset time interval. The Ton instruction begins to count time base intervals when the rung conditions become true.

- The accumulated value is reset when the rung condition go false regardless of whether the timer has timed out

#### Instruction parameter- Timer TON is 3 word element.

|      | 1            |       |                           |     |

|------|--------------|-------|---------------------------|-----|

|      |              | 14    | 13 12 11 10 9 8 7 6 5 4 3 |     |

|      | 15           | 2 1 0 |                           |     |

| word |              |       |                           | 16  |

| 0    | TT\EN        | TT\EN | DN                        | bit |

| word |              |       |                           | 16  |

| 1    | preset value |       |                           | bit |

| word | Accumulato   |       |                           | 16  |

| 2    | r value      |       |                           | bit |

#### Status bit explanation-

- i) **Timer done bit (bit13)-**DN is set when the accumulated value is equal to or greater than the preset value. It is reset when rung condition become false.

- ii) **Timer enable bit (bit 14)-**EN is set when rung condition are true. It is reset when rung condition become false.

- iii) Timer timing bit (bit15)-TT is set when rung conditions are true & the accumulated value is less than the preset value. It is reset when the rung conditions go false or when the done bit is set.

#### (ii) OFF delay timer

- This instruction counts time interval when conditions preceding it in the rung are false. Produces low output when accumulated value reaches the preset value.

- Use Toff instruction to turn an output on or off after the timer has been off for a preset timer has been off for a preset time intervals. The Toff instruction begins to count time base intervals when the rung makes a true to false to transition.

- As long as rung conditions remains false the timer increments its accumulated value each scan until it reaches the preset value. The accumulated value is reset when the rung conditions go true regardless of whether the timer has timed out.

Instruction parameter- Timer TOFF is 3 word element.

02 marks

#### **WINTER - 15 EXAMINATION**

|      | 14   13   12   11   10   9   8   7   6   5   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----|

| iv)  | Develop ladder diagram for logic operation a) OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | 04 |

| Ans. | b) EX-OR i. OR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2           |    |

| Alls | Inputs    OR truth table   Inputs   Output   A B Y   Output   A B   Output   Output   A B   Output   Out | Marks.      |    |

|      | c) EX-OR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>Marks. |    |

### **WINTER - 15 EXAMINATION**

|      | <del>,</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                            |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|

|      | Inputs  Output  Output  Output  A B Y  O O O O  O 1 1  1 0 1  1 1 0 1  1 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |    |

|      | Fig- The EX-OR gate symbol and truth table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              |    |

|      | Ladder logic program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |    |

|      | A B Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                              |    |

| Q4B  | Attempt any ONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              | 06 |

| i)   | Describe the wiring details of AC output module of PLC with diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              | 06 |

| Ans. | The below fig show the basic field wiring for digital 120V AC output module. The Wiring diagrams show how wires of output devices are connected to screw terminals of PLC modules. As per the wiring diagram, User has to connect the wires of input and output devices to PLC or Module.  It can be thought of as a simple switch power can be provided to control the output device. During normal operation, processor sends the output state that was determined by logic diagram of output module. The module then switches the power to the field devices. A fuse is normally provided in that the output circuit of the module to prevent excessive current from damaging the wiring to the field devices. | Descrip<br>tion- 04<br>Mark, |    |

|      | Output module  120V ac Input  0 Heater 1 H1  1 Heater 2 H2  Screw terminals  3 Pump starter  N Neutral  Typical discrete output module wiring diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Diagra<br>m- 02<br>Marks     |    |

#### **WINTER - 15 EXAMINATION**

Subject Code: 17536

| ii)  | Explain the PD control action w. r. t. eqn and response. State their advantage and drawback.                                                                                                                                                                                                                                                                                                                                                                                                     |                             | 06  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|

| Ans. | <ul> <li>PD control action mode is used in industrial applications. It uses proportional and derivative modes serially. Mathematically it is given by;</li> <li>P = K<sub>p</sub> e (t) + K<sub>p</sub> K<sub>D</sub> de (t)/dt + p (0)</li> <li>Above equation contains three mathematical terms i.e. K<sub>p</sub> e (t) indicates the proportional output term,</li> <li>K<sub>p</sub> K<sub>D</sub> de (t)/dt indicates derivative term and p(0) controller output with no error.</li> </ul> | Descrip<br>tion- 2<br>Mark, |     |

|      | e(t)[%]  (+)  O  (-)  P(%)  Proportional response  Derivative response                                                                                                                                                                                                                                                                                                                                                                                                                           | Respons<br>e- 2<br>Mark,    |     |

|      | Fig- Proportional-Derivative action. Advantages-                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |     |

|      | <ul> <li>i. It allows the rise of narrower proportional band with its lesser offset.</li> <li>ii. Increases the controller gain during the error changes.</li> <li>iii. Can compensate the rapidly changing error.</li> <li>iv. Can handle the fast processes.</li> <li>v. Can compensate some of the lag in a process.</li> </ul>                                                                                                                                                               | Adv 1<br>mark               |     |

|      | Disadvantages-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Disadv-                     |     |

|      | It cannot eliminate offset of proportional controller.                                                                                                                                                                                                                                                                                                                                                                                                                                           | 01Mark                      | 4.6 |

| Q. 5 | Attempt any TWO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             | 16  |

| a)   | Consider sixth order system with characteristic equation $s^6 + 2s^5 + 8s^4 + 12s^3 + 20s^2 + 16s + 16 = 0$ . Determine stability                                                                                                                                                                                                                                                                                                                                                                |                             | 08  |

|      | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |     |