| WINTER-17 EXA | MINATION |

|---------------|----------|

| Model Ar      | nswer    |

Subject Code:

**Subject Name: Digital Techniques**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q. N. | Answer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Marking<br>Scheme                                                                                                                           |

|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1.        | (a)          | Attempt any six of the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 Marks                                                                                                                                    |

|           | i)           | List any two advantage and disadvantage of digital circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2M                                                                                                                                          |

|           | Ans:         | <ul> <li>Advantages:</li> <li>Digital circuits are highly reliable and accurate.</li> <li>They are small in size and the speed of operation is very high.</li> <li>Digital ICs can be programmable.</li> <li>The effect of fluctuations in the characteristics of the components, ageing of components, temperature, and noise etc. is very small in digital circuits.</li> <li>Digital circuits have capability of memory which makes these circuits highly suitable for computers, calculators, watches, telephones etc.</li> </ul> | (Any two<br>Advantage<br>s: <sup>1</sup> / <sub>2</sub> mark<br>each, Any<br>two<br>disadvanta<br>ges : <sup>1</sup> / <sub>2</sub><br>mark |

|           | ii)          | <ul> <li>Disadvantages:</li> <li>If there is a loss of digital data in a transmission, there will be error and misinterpretation of data.</li> <li>All real world signals are analog in nature. So it is necessary to convert these signals into digital to process digitally. This requires additional circuitry</li> <li>Define fan in and noise margin.</li> </ul>                                                                                                                                                                 | each)                                                                                                                                       |

|           | ,<br>,       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                             |

|           | Ans:         | <ul><li>Fan in: The number of inputs that a logic gate can handle.</li><li>Noise margin: The difference between the tolerable output and input voltage ranges is called the noise margin of the gate.</li></ul>                                                                                                                                                                                                                                                                                                                       | (Definition<br>s: 1 mark<br>each)                                                                                                           |

| iii) | Simplify using Boolean algebra (A+B) (A+C).                                                                                                                                                                                                                                                                                                                                                                        | <b>2M</b>                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Ans: | (A+B)(A+C) = AA + AC + AB + BC                                                                                                                                                                                                                                                                                                                                                                                     | (2 marks)                                      |

|      | =A + AB + AC + BC (Since A.A = A)                                                                                                                                                                                                                                                                                                                                                                                  |                                                |

|      | = A (1+B+C) + BC (Since 1+B+C = 1)                                                                                                                                                                                                                                                                                                                                                                                 |                                                |

|      | = A + BC                                                                                                                                                                                                                                                                                                                                                                                                           |                                                |

| iv)  | Draw symbol, truth table and logic equation of EX-NOR gate.                                                                                                                                                                                                                                                                                                                                                        | 2M                                             |

| Ans: |                                                                                                                                                                                                                                                                                                                                                                                                                    | (Symbol:<br>(1/2<br>mark,<br>Truth<br>Table: 1 |

|      | Truth Table:                                                                                                                                                                                                                                                                                                                                                                                                       | mark,                                          |

|      | InputsOutputABY = $\overline{A \oplus B}$                                                                                                                                                                                                                                                                                                                                                                          | Logic<br>Equation<br><sup>1</sup> ⁄2 mark)     |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |

|      | 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |

|      | 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |

|      | 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |

|      | Logic Equation:                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |

|      | $Y = A \cdot B + \overline{A} \cdot \overline{B}$                                                                                                                                                                                                                                                                                                                                                                  |                                                |

|      | $\mathbf{Y} = \mathbf{\overline{A} \oplus B}$                                                                                                                                                                                                                                                                                                                                                                      |                                                |

| v)   | Define minterm and maxterm.                                                                                                                                                                                                                                                                                                                                                                                        | 2M                                             |

| Ans: | Minterm: A minterm, denoted as mi, where $0 \le i < 2^n$ , is a product (AND) of the n variablesin which each variable is complemented if the value assigned to it is 0, and uncomplementedif it is 1.Maxterm: A maxterm, denoted as Mi, where $0 \le i < 2^n$ , is a sum (OR) of the n variables(literals) in which each variable is complemented if the value assigned to it is 1, anduncomplemented if it is 0. | (minterm<br>and<br>maxterm<br>:1mark<br>each)  |

| vi)  | Draw symbol and truth table of T-flip-flop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2M                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Ans: | Symbol:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (Symbol: 1<br>mark,<br>Truth<br>table: 1<br>mark) |

|      | InputsOutputsCommentsET $Q_{rest}$ $\overline{Q}_{rest}$ 10 $Q_r$ $\overline{Q}_r$ No change11 $\overline{Q}_r$ $Q_r$ Toggle                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |

| vii) | What is the difference between edge Triggering and level Triggering (any 2)?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2M                                                |

| Ans: | Edge TriggeringLevel TriggeringA logical circuit whose output<br>changes during the positive or<br>negative transition of the clock is<br>called edge triggeringA logical circuit whose output<br>changes during 0 level or 1<br>level of the clock is called<br>level triggeringIt is instantaneous in natureThe output changes during a<br>certain definite pulse duration<br>of the clockTriggers on this edge<br>of the clock pulseTriggers on high dock levelTriggers on this edge<br>of the clock pulseTriggers on high dock levelHigh Level TriggeringHigh Level Triggering | (1 mark<br>each)                                  |

|      | Triggers on this edge<br>of the clock pulse<br>CLK<br>Q<br>Negative Edge Triggering<br>Triggers on low clock level<br>CLK<br>Q<br>Low Level Triggering                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |

| viii)        | State two specification of DAC                                                                                          | <b>.</b>        |                     |             |           |                  |      |                 | 2M                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|-------------|-----------|------------------|------|-----------------|------------------------------------------|

| Ans:         | Specifications of DAC:<br>Resolution<br>Settling time<br>Linearity<br>Accuracy                                          |                 |                     |             |           |                  |      |                 | (Any 2<br>specifica<br>on: 1 ma<br>each) |

| ( <b>b</b> ) | Attempt any two of the follow                                                                                           | ing:            |                     |             |           |                  |      |                 | 8 Mark                                   |

| i)           | Perform the following operati<br>a) 10110 – 1010 using 1' <sup>s</sup> cor<br>b) 11010 – 11110 using 2 <sup>nd</sup> co | nplem           |                     |             |           |                  |      |                 | 4M                                       |

| Ans:         |                                                                                                                         | plements in the | n <b>t i</b><br>e n | met<br>ninu | ho<br>ien | <b>d:</b><br>d a | nd s | ubtrahend equal | (2 marl<br>each)                         |

|              | Step 3: Adding 10110 to 0101                                                                                            |                 |                     | 1           | 0         | 1                | 1    |                 |                                          |

|              |                                                                                                                         |                 |                     |             | 0         | 1                | 1    | 0               |                                          |

|              | +                                                                                                                       | Carry           | 1                   |             | 1         | 1                | 0    |                 |                                          |

|              |                                                                                                                         |                 | 1                   |             | 1         | 0                | 1    | 1               |                                          |

|              | Step 4: Since final carry is gene                                                                                       |                 |                     |             |           |                  |      | -               |                                          |

|              |                                                                                                                         |                 |                     | 0 1         | 0         | 1                | 1    |                 |                                          |

|              |                                                                                                                         | +               | 1                   |             |           |                  | 1    | -               |                                          |

|              |                                                                                                                         | Carry           |                     |             | 1         | 1                |      |                 |                                          |

|              |                                                                                                                         | =               |                     | 1           | 1         | 0                | 0    | -               |                                          |

|              | 10110-1010 = 1100                                                                                                       |                 |                     |             |           |                  |      | _               |                                          |

|              | b) 11010 – 11110 using 2 <sup>nd</sup> of<br>The number of bits in minuend<br>Step I: Obtain 2's comp                   | and su          | bt                  | rahe        | end       | are              |      | ıal             |                                          |

|              | 1's complement of (111                                                                                                  | 10) 1           | 11                  | 10          |           |                  |      |                 |                                          |

|              |                                                                                                                         | C               | 00                  | 01          |           |                  |      |                 |                                          |

|              |                                                                                                                         |                 |                     |             |           |                  |      |                 |                                          |

|              |                                                                                                                         |                 |                     |             |           |                  |      |                 |                                          |

Adding 1to 00001

|       | 0 | 0 | 0 | 0 | 1 |

|-------|---|---|---|---|---|

| +     |   |   |   |   | 1 |

| Carry |   |   |   | 1 |   |

| =     | 0 | 0 | 0 | 1 | 0 |

| 1     |   |   |   |   |   |

Step II: Adding 11010 to 00001

|       | 1 | 1 | 0 | 1 | 0 |

|-------|---|---|---|---|---|

| +     | 0 | 0 | 0 | 1 | 0 |

| Carry |   |   | 1 |   |   |

| =     | 1 | 1 | 1 | 0 | 0 |

Step III: Since no carry is generated, the answer is negative and in 2's compliment form

Finding 2's compliment of 11100

|      |                              |        |       |                  | 1    | 1    | 1    | 0           | 0    |                  |                         |

|------|------------------------------|--------|-------|------------------|------|------|------|-------------|------|------------------|-------------------------|

|      |                              | 1's c  | comj  | oliment          | 0    | 0    | 0    | 1           | 1    |                  |                         |

|      |                              | +      |       |                  |      |      |      |             | 1    |                  |                         |

|      |                              | Carr   | У     |                  |      |      | 1    | 1           |      |                  |                         |

|      |                              |        |       |                  | 0    | 0    | 1    | 0           | 0    |                  |                         |

|      |                              |        | 110   | 10-1111          | 0 =  | (-0  | 010  | )()         |      |                  |                         |

| ii)  | State and verify De-Mo       | rgan's | s fir | st theore        | em i | ısin | g t  | rut         | h ta | ble.             | <b>4M</b>               |

| Ans: | It states that the, complete | nent o | f a s | um is eq         | ual  | to p | oroc | luct        | of   | heir complements | (Statement<br>: 1 mark, |

|      |                              | А      | В     | $\overline{A+B}$ | Ā    | B    | Ā    | ī. <u>B</u> |      |                  | Verificatio<br>n: 3     |

|      |                              | 0      | 0     | 1                | 1    | 1    |      | 1           |      |                  | marks)                  |

|      |                              | 0      | 1     | 1                | 1    | 0    |      | 1           |      |                  |                         |

|      |                              | 1      | 0     | 1                | 0    | 1    |      | 1           |      |                  |                         |

|      |                              | 1      | 1     | 0                | 0    | 0    |      | 0           |      |                  |                         |

|      |                              |        |       |                  |      |      |      |             |      |                  |                         |

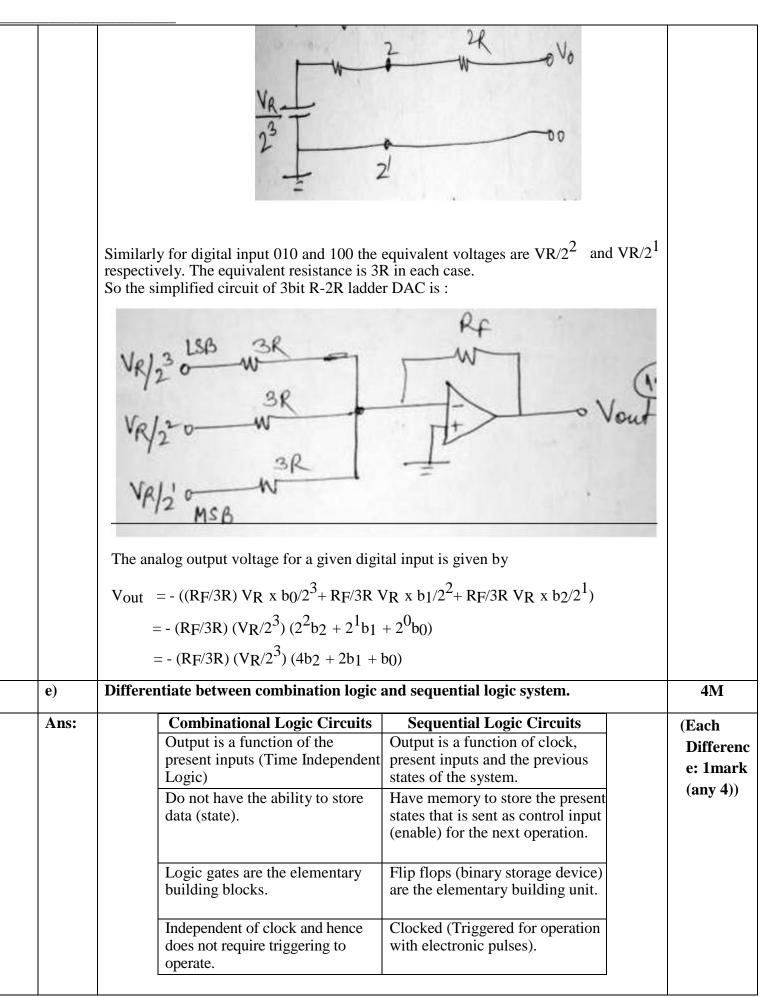

|    | iii) | Compare R-2R and weighted resistor DAC any four points.                                                                                                                                                                                                                                                                                               | 4M                            |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|    | Ans: | Weighted resistor DAC     R-2R ladder DAC                                                                                                                                                                                                                                                                                                             | (1 mark<br>each)              |

|    |      | It requires more than two resistorIt requires resistors of only two<br>values.                                                                                                                                                                                                                                                                        |                               |

|    |      | To get precise high value resistor<br>is difficultSince same 2 value resistors are<br>used, the precision of resistors is not<br>a problem                                                                                                                                                                                                            |                               |

|    |      | It requires one resistor per bit It requires two resistor per bit                                                                                                                                                                                                                                                                                     |                               |

|    |      | It is not possible to expand       It can be easily expanded to handle more number of bits by adding resistors                                                                                                                                                                                                                                        |                               |

| 2. |      | Attempt any four of the following:                                                                                                                                                                                                                                                                                                                    | 16 Marks                      |

|    | a)   | Reduce the following logic expression using Boolean laws and De- Morgan's<br>theorems. $Y = \overline{A.(\overline{A.B})}$ $\overline{B.(\overline{A.B})}$                                                                                                                                                                                            | 4M                            |

|    | Ans: | $Y = \overline{A.(\overline{A.B})} \cdot \overline{B.(\overline{A.B})}$ $Y = (\overline{A} + \overline{\overline{AB}}) (\overline{B} + \overline{\overline{AB}}) (Applying De Morgan's Theorems)$ $Y = (\overline{A} + AB)(\overline{B} + AB)^{*} (By applying the Boolean law A + \overline{A}B = A + B)$ $Y = (\overline{A} + B)(A + \overline{B})$ | (1 marks<br>for each<br>step) |

| b)            | Convert the following                                              |                                                         |                              |       | <b>4</b> M          |  |  |

|---------------|--------------------------------------------------------------------|---------------------------------------------------------|------------------------------|-------|---------------------|--|--|

| Ans:          | i) (6AC) <sub>16</sub> = (?) <sub>10</sub><br>{**Note: Step markin | $\frac{\text{ii}) (372)_8}{\text{g should be given n}}$ | (?) <sub>2</sub><br>narks**} |       | (2 marks            |  |  |

| <b>A</b> 115. | i) $(6AC)_{16} = 6x \ 16^2 + 3$                                    |                                                         |                              |       | for each<br>correct |  |  |

|               | = 6 x 256 + 160 + 1                                                | 2                                                       |                              |       | Conversio<br>n)     |  |  |

|               | = 1536 + 160 + 12                                                  |                                                         |                              |       |                     |  |  |

|               | = 1708                                                             |                                                         |                              |       |                     |  |  |

|               | $(6AC)_{16} = (1708)_{10}$                                         |                                                         |                              |       |                     |  |  |

|               | ii)(372) <sub>8</sub> = (?)                                        |                                                         |                              |       |                     |  |  |

|               | Binary equivalent of 3                                             | is 011                                                  |                              |       |                     |  |  |

|               | Binary equivalent of 7                                             | is 111                                                  |                              |       |                     |  |  |

|               | Binary equivalent of 2                                             | is 010                                                  |                              |       |                     |  |  |

|               | $(372)_8 = (011\ 111\ 010)$                                        | )2                                                      |                              |       |                     |  |  |

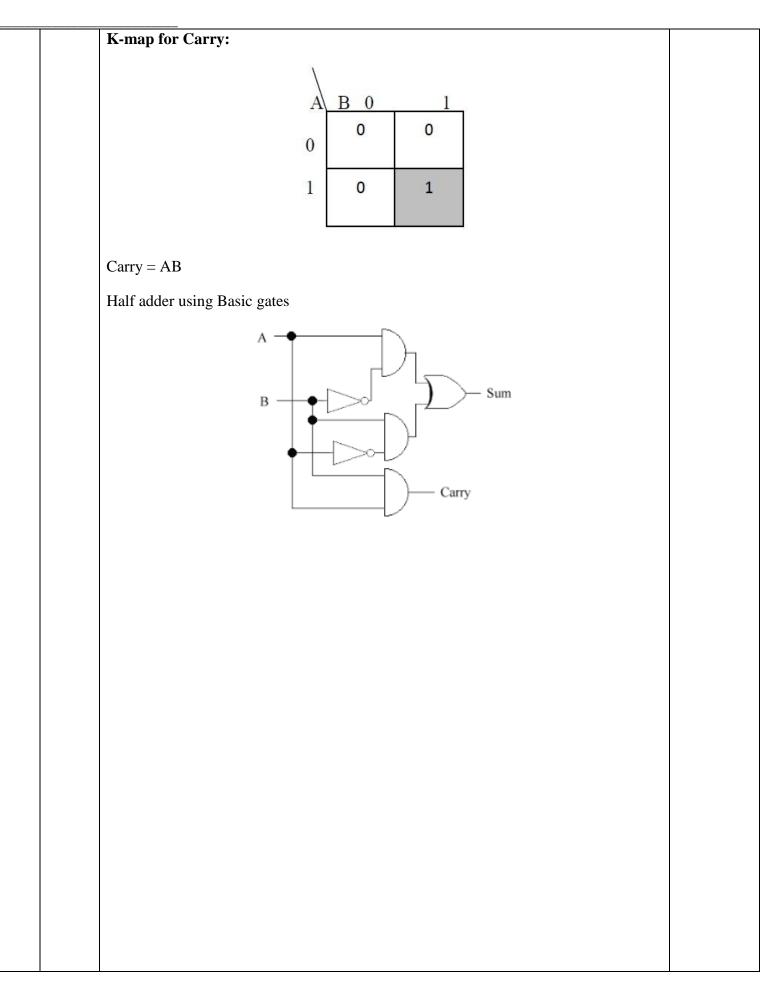

| <b>c</b> )    | Design Half adder usi                                              | Design Half adder using K-map and basic gates.          |                              |       |                     |  |  |

| Ans:          | Truth Table:                                                       |                                                         |                              |       | (Truth<br>table:    |  |  |

|               | INPU                                                               | TS                                                      | OU                           | TPUTS | 1 1mark, 1          |  |  |

|               | A                                                                  | В                                                       | SUM                          | CARRY | mark each           |  |  |

|               | 0                                                                  | 0                                                       | 0                            | 0     | k map,              |  |  |

|               | 0                                                                  | 1                                                       | 1                            | 0     | 1mark               |  |  |

|               | 1                                                                  | 0                                                       | 1                            | 0     | circuit)            |  |  |

|               | 1                                                                  | 1                                                       | 0                            | 1     |                     |  |  |

|               | K map                                                              |                                                         |                              |       |                     |  |  |

|               | K-map for Sum:                                                     |                                                         |                              |       |                     |  |  |

|               |                                                                    | A B 0                                                   | 1                            |       |                     |  |  |

|               |                                                                    |                                                         | 1                            |       |                     |  |  |

|               |                                                                    | 0 0                                                     | 1                            |       |                     |  |  |

|               |                                                                    | 1                                                       | 0                            |       |                     |  |  |

|               | $Sum = \overline{A} B + A \overline{B}$                            |                                                         |                              |       |                     |  |  |

\_\_\_\_

| Draw 8: 1 multiplexer using basic lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | gic gates.                                                                                                                                                                                                                                              | 4M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| {**Note: Equation optional**}<br>$ \begin{cases} x^{2} \\ x^{3} \\ x^{3} \\ x^{3} \\ x^{3} \\ x^{3} \\ x^{3} \\ x^{4} \\ x^{5} \\ x^$ | D<br>OUTPUT<br>Y<br>E<br>SI SO D3+<br>SI SO D3+<br>SI SO D3+<br>SI SO D3+                                                                                                                                                                               | (Diagram:<br>4 marks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Compare RAM and ROM any four                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | point.                                                                                                                                                                                                                                                  | 4M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Random Access Memory or RAM<br>is a form of data storage that can be<br>accessed randomly at any time, in<br>any order and from any physical<br>location, allowing quick access and<br>manipulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Read-only memory or ROM is also a form<br>of data storage that cannot be easily altered<br>or reprogrammed. Stores instructions that<br>are not necessary for re-booting to make the<br>computer operate when it is switched off.<br>They are hardwired | (Four<br>points:1<br>mark<br>each)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RAM allows the computer to read<br>data quickly to run applications. It<br>allows reading and writing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ROM stores the program required to initially<br>boot the computer. It only allows reading                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RAM is volatile i.e. its contents are lost when the device is powered off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | It is non-volatile i.e. its contents are retained<br>even when the device is powered off.                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| The two main types of RAM are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The types of ROM include PROM, EPROM                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <pre>{**Note: Equation optional**}  \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$</pre>                                                                                                                                                         | {**Note: Equation optional**}         \$2         \$2         \$1         \$2         \$2         \$1         \$2         \$2         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3         \$3 |

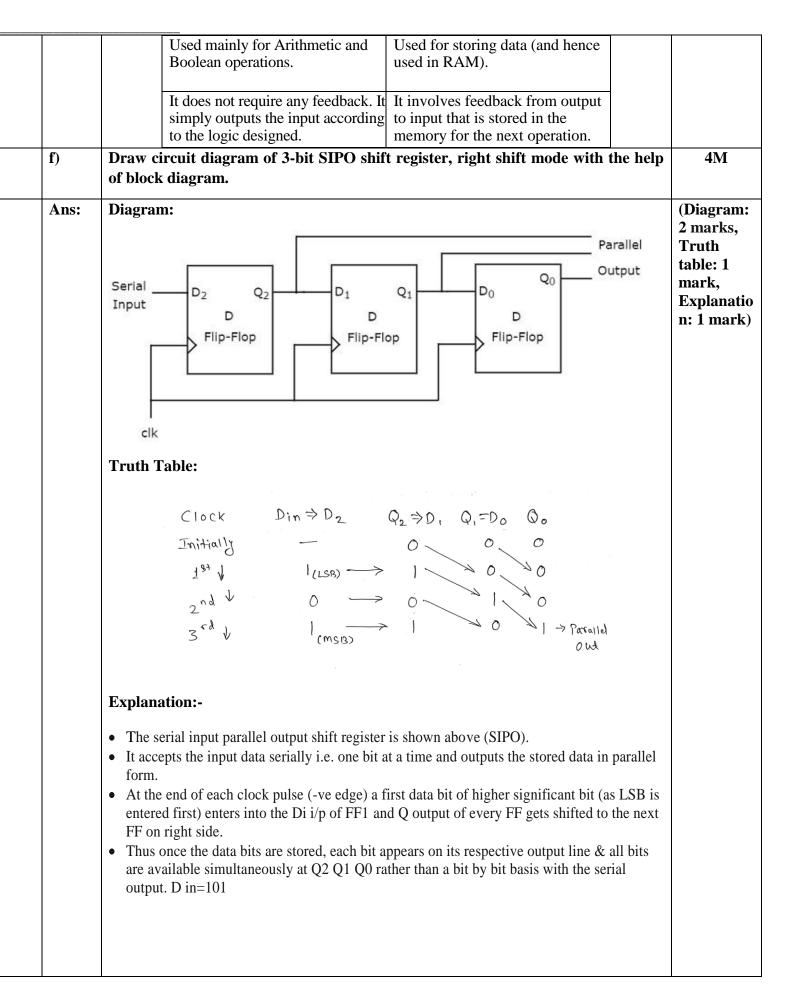

| <b>f</b> ) | Draw logic diagram of JK-flop-flop and write its truth table.                                                                                                                                                                                                                                                                                                  | <b>4M</b>                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Ans:       | Logic Diagram:                                                                                                                                                                                                                                                                                                                                                 | (Logic<br>Diagram:2<br>marks,<br>Truth<br>Table :2<br>marks) |

|            | InputsOutput $J_n$ $K_n$ $Q_{n+1}$ $0$ $0$ $Q_n$ $1$ $0$ $1$ $0$ $0$ $1$ $1$ $1$ $\overline{Qn}$                                                                                                                                                                                                                                                               |                                                              |

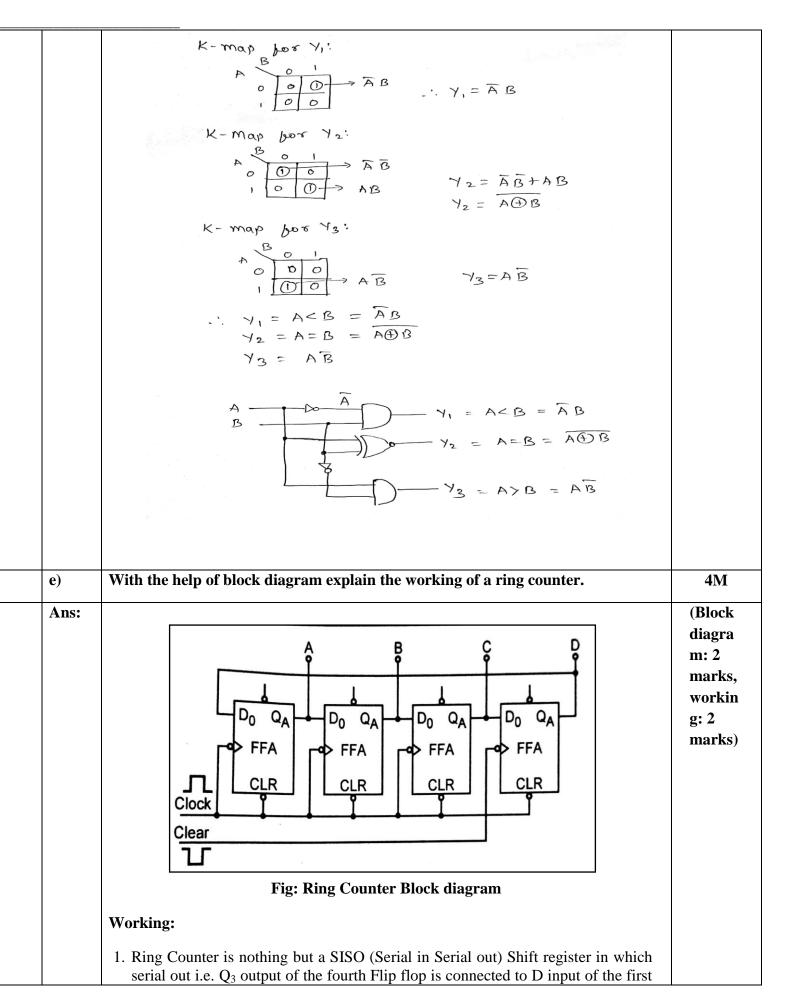

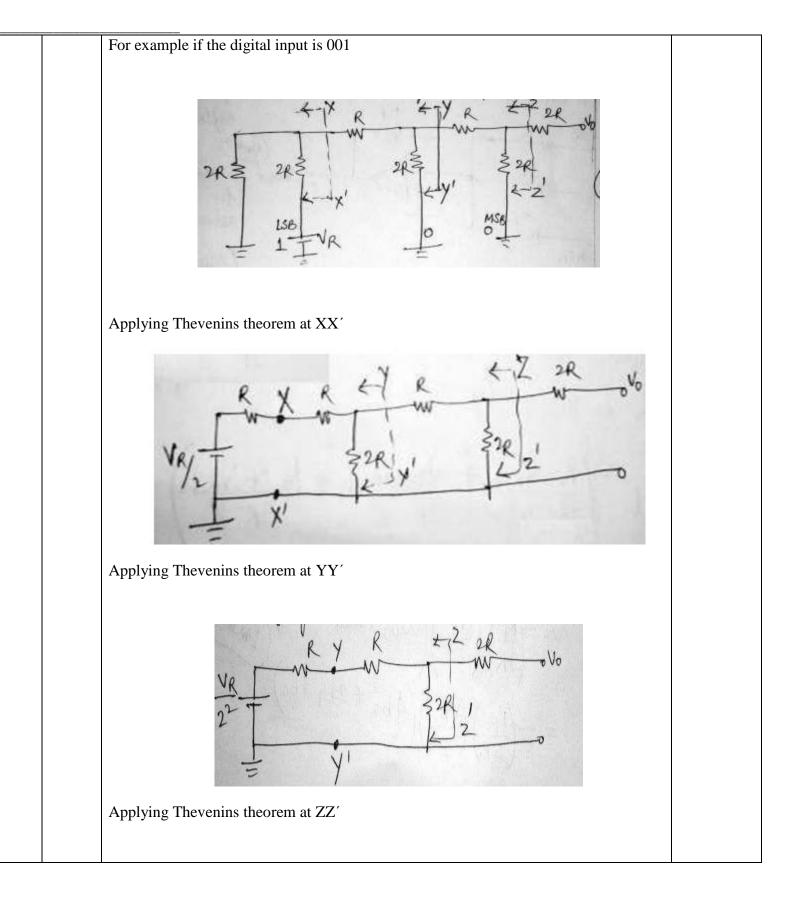

|            | Attempt any four of the following:                                                                                                                                                                                                                                                                                                                             | 16 Marks                                                     |

| a)         | i) $(637)_{10} + (463)_{10}$ ii) $(63)_{10} + (19)_{10}$                                                                                                                                                                                                                                                                                                       | 4M                                                           |

| Ans:       | $\{\text{**Note: Steps marking should be given marks**}\}$ i) $\binom{(673)_{10} \Rightarrow 0110 0111 0011}{+ (463)_{10} \Rightarrow 0100 0110 0011}$ $\frac{1010}{1101 0110} \frac{1101}{0110} 1102 0110}{1101 0110} \text{ invalid} BCD$ $\frac{1}{1} \frac{0001}{001} \frac{0011}{0110} \frac{0110}{6}$ $\therefore (673)_{10} + (463)_{10} = (1136)_{10}$ | (Correct<br>answer:<br>2 marks<br>each)                      |

|      | ii)                                                                                                                                                                                                                                                    |                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

|      | $(63)_{10} \Rightarrow 0110 0011 + (19)_{10} \Rightarrow 0001 1001 0111 100 invalid BCD 1000 0010 \\ 1000 0010 \\ 8 2 2$                                                                                                                               |                                                       |

|      | $(63)_{10} + (19)_{10} = (82)_{10}$                                                                                                                                                                                                                    |                                                       |

| b)   | What is an Universal gate? Prove NAND as an universal gate.                                                                                                                                                                                            | <b>4</b> M                                            |

| Ans: | NAND and NOR gates are called as Universal Gates because it is possible to implement any Boolean expression with the help of only NAND or NOR gates, Hence, a user can build any combinational; circuit with the help of only NAND gates or NOR gates. | (Univers<br>l gate: 2<br>marks,<br>Proof: 2<br>marks) |

|      | Proof:                                                                                                                                                                                                                                                 | marks)                                                |

|      | Using NAND gates, OR, AND and NOT gates may be constructed as shown below<br>NAND as OR Cate.                                                                                                                                                          |                                                       |

|      | $A = \boxed{D_{0}} = \boxed{\overline{A} \cdot \overline{B}} = A + B.$ $B = \boxed{D_{0}} = \boxed{\overline{B}}$                                                                                                                                      |                                                       |

|      | Ā.B = Ā + B = A + B.<br>NAND AS NOT gate.                                                                                                                                                                                                              |                                                       |

|      | $A = \Box \bigcirc A \cdot A = A$                                                                                                                                                                                                                      |                                                       |

|            |                                                  | -: [<br>/                                                              | $Y = \overline{A}$ $Y = A$ $\overline{A}$ $\overline{Fig}$                                  |                                                                                                                                                                                                                                                                                      | $(: \overline{A} = )$<br>$\rightarrow Y = \overline{A} \overline{B}$<br>te using                                              | 3                                                                                          |                                                                                                           |

|------------|--------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| <b>c</b> ) | Design 1:8 I                                     | De-mult                                                                | tiplexer                                                                                    | using 1:4 demu                                                                                                                                                                                                                                                                       | ıltiplexer.                                                                                                                   |                                                                                            | 4M                                                                                                        |

| Ans:       |                                                  |                                                                        | D <sub>in</sub><br>A<br>B<br>C                                                              |                                                                                                                                                                                                                                                                                      | L : 4<br>CMUX<br>S0<br>S0<br>1 : 4<br>EMUX                                                                                    | Y0<br>Y1<br>Y2<br>Y3<br>Y4<br>Y5<br>Y6<br>Y7                                               | (Design<br>ing: 4<br>marks)                                                                               |

|            |                                                  |                                                                        | ΛR                                                                                          | C are the select                                                                                                                                                                                                                                                                     |                                                                                                                               | -                                                                                          |                                                                                                           |

|            |                                                  |                                                                        |                                                                                             | C are the select                                                                                                                                                                                                                                                                     | line inputs                                                                                                                   |                                                                                            |                                                                                                           |

|            |                                                  |                                                                        | g: 1:8 De                                                                                   | e-multiplexer u                                                                                                                                                                                                                                                                      | line inputs sing 1:4 De-mu                                                                                                    | ltiplexer                                                                                  |                                                                                                           |

| d)         |                                                  | compa                                                                  | g: 1:8 De<br>trator us                                                                      | e-multiplexer u<br>ing K-map and                                                                                                                                                                                                                                                     | line inputs<br>sing 1:4 De-mu<br>l draw its logic                                                                             | ltiplexer<br>diagram.                                                                      | 4M                                                                                                        |