# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

Subject Code: 17319

## **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in themodel answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may tryto assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given moreImportance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for anyequivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| ).<br>וס. | Sub<br>Q. N. | Answers                |                                   |                                                                                                                                                     |               | Marking<br>Scheme  |  |

|-----------|--------------|------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|--|

|           | A            | Attempt any SIX:       |                                   |                                                                                                                                                     |               | 12- Total<br>Marks |  |

|           | а            | List different operati | ng regions of transist            | or.                                                                                                                                                 |               | 2M                 |  |

|           | Ans:         | Operating regions of   | transistor:-                      |                                                                                                                                                     |               | 2M                 |  |

|           |              | Operating Region       | I <sub>B</sub> or V <sub>CE</sub> | BC and BE junctions                                                                                                                                 | Mode          |                    |  |

|           |              | Cut off                | I <sub>B</sub> =very small        | Reverse biased and<br>Reverse biased                                                                                                                | Open switch   |                    |  |

|           |              | Saturation             | V <sub>CE</sub> = Very small      | Forward biased and<br>Forward biased                                                                                                                | Closed switch |                    |  |

|           |              | Active                 | V <sub>CE</sub> = Moderate        | Reverse biased and<br>Forward biased                                                                                                                | Amplifier     |                    |  |

|           | b            | Define the term stab   | ility factor.                     |                                                                                                                                                     |               | 2M                 |  |

|           | Ans:         |                        | eeping both the curre             | etor current I <sub>c</sub> with respense<br>ent I <sub>B</sub> and the current gain<br>$= \frac{dI_c}{dI_{co}} = \frac{\Delta I_c}{\Delta I_{co}}$ |               | 2M                 |  |

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

| С    | Draw the symbol of n-channel and p-channel JFET.                                                       | 2M         |

|------|--------------------------------------------------------------------------------------------------------|------------|

| Ans: | Symbol of n-channel and p-channel JFET:-                                                               | 1M each    |

|      | Schematic Symbol Schematic Symbol                                                                      |            |

|      | of an <i>n</i> -Channel JFET of a <i>p</i> -Channel JFET                                               |            |

|      |                                                                                                        |            |

|      | G G                                                                                                    |            |

|      | ♦ S ♦ S                                                                                                |            |

| d    | List the types of amplifier coupling.                                                                  | 2M         |

| Ans: | Types of amplifier coupling: (ANY TWO)                                                                 | 1M each    |

|      | 1. Resistance – capacitance (RC) coupling.                                                             |            |

|      | 2. Transformer coupling                                                                                |            |

|      | 3. Direct coupling                                                                                     |            |

| е    | Define intrinsic stand-off ratio of UJT.                                                               | 2M         |

| Ans: | Intrinsic standoff ratio:                                                                              | (Definitio |

|      | It is defined as the ratio of the $R_{B1}$ (base resistance 1) to the inter-base resistance $R_{BB}$ . | :1M,       |

|      | $R_{B_1} = R_{B_1}$                                                                                    | Equation   |

|      | $I_{I} = \frac{1}{R_{BB}} = \frac{1}{R_{B1} + R_{B2}}$                                                 | :1M)       |

| f    | State the need of voltage regulator.                                                                   | 2M         |

| Ans: | NEED OF VOLTAGE REGULATORS:-                                                                           | 2M         |

|      | DC voltage obtained by using rectifier and filter is not constant and may vary depending               |            |

|      | upon supply variations. This DC voltage may result in an error or may damage other                     |            |

|      | electronic devices or circuits                                                                         |            |

|      | e.g.                                                                                                   |            |

|      | 1. In oscillators it may lead to phase shift.                                                          |            |

|      | 2. In amplifiers it may lead to change in voltage gain or power gain.                                  |            |

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

|      | 4. It may produce distortions in output of audio and video amplifiers.                                                                                                                                                                                                                                    |                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|      | Hence to avoid these errors DC voltage regulators are necessary to keep the output DC                                                                                                                                                                                                                     |                   |

|      | voltage constant.                                                                                                                                                                                                                                                                                         |                   |

| g    | Define efficiency of power amplifier.                                                                                                                                                                                                                                                                     | 2M                |

| Ans: | Definition:-                                                                                                                                                                                                                                                                                              | 1M                |

|      | Efficiency of power amplifier is defined as the ratio of r.m.s. output power dissipated in the load to the total DC power taken from the supply source.                                                                                                                                                   | 1M                |

|      | Formula:-                                                                                                                                                                                                                                                                                                 |                   |

|      | $\eta\% = \frac{P_{OUT}}{P_{DC}} \times 100$                                                                                                                                                                                                                                                              |                   |

|      | Where:                                                                                                                                                                                                                                                                                                    |                   |

|      | $\eta\%$ – is the efficiency of the amplifier.                                                                                                                                                                                                                                                            |                   |

|      | Pout – is the amplifiers output power delivered to the load.                                                                                                                                                                                                                                              |                   |

|      | Pdc – is the DC power taken from the supply.                                                                                                                                                                                                                                                              |                   |

| h    | State the condition for sustained oscillations.                                                                                                                                                                                                                                                           | 2M                |

| Ans: | Conditions for sustained oscillations:-                                                                                                                                                                                                                                                                   | 1M each           |

|      | <ol> <li>The total shift introduced, as the signal proceeds from input terminals through the amplifier and feedback network &amp; back again to the input is precisely 0° or 360°.</li> <li>The magnitude of the loop gain A<sub>Vβ</sub> must be equal to 1 at the frequency of oscillations.</li> </ol> |                   |

|      | $A_{V}\beta = 1 \& \theta = 0^{\circ} \text{ or } 360^{\circ}.$                                                                                                                                                                                                                                           |                   |

| В    | Attempt any TWO:                                                                                                                                                                                                                                                                                          | 8- Total<br>Marks |

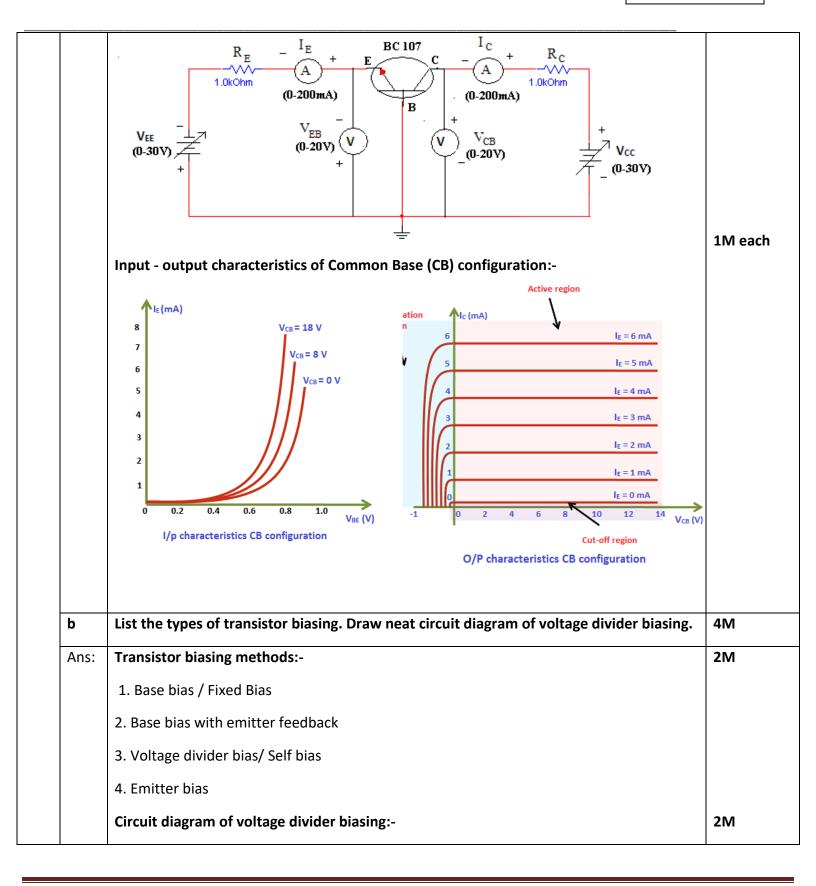

| a    | Draw the circuit diagram for Common Base (CB) configuration and draw its input and output characteristics.                                                                                                                                                                                                | 4M                |

| -    |                                                                                                                                                                                                                                                                                                           |                   |

### **SUMMER-18 EXAMINATION**

Subject Code: 17319

Subject Name: Electronic Devices & Circuits Model Answer

V<sub>cc</sub> **≷** R₁ Rc≩ l I<sub>C</sub> BE RE Draw and explain zener diode as a voltage regulator. 4M С Ans: Circuit diagram:-Fixed (a) Varying input voltage. 1M Part I: REGULATION BY VARYING INPUT VOLTAGE: diagram, 1M A resistance (R<sub>s</sub>) is connected in series with the zener diode to limit current in the circuit. **Explanation** For proper operation, the input voltage (Vs) must be greater than the zener voltage (Vz). Where, R<sub>z</sub>= zener resistance  $|_{s} = |_{7} + |_{1}$ Here the load resistance is kept fixed and input voltage is varied within the limits Case1:- WHEN INPUT VOLTAGE IS INCREASED When input voltage is increased the input current (Is) also increases. Thus current through zener diode gets increased without affecting the load current(IL). The increase in input voltage also increases the voltage drop across the resistance Rs thereby keeping the V<sub>L</sub> constant. **Case 2:- WHEN INPUT VOLTAGE IS DECREASED**

Subject Name: Electronic Devices & Circuits Model Answer

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

| Q.<br>No | Sub<br>Q.<br>N. | Answers                                                                                          | Marking<br>Scheme  |

|----------|-----------------|--------------------------------------------------------------------------------------------------|--------------------|

| 2        |                 | Attempt any FOUR:                                                                                | 16- Total<br>Marks |

|          | а               | Describe the concept of thermal runaway. How it should be avoided?                               | 4M                 |

|          | Ans             | Concept of thermal Runaway:-                                                                     | 3M                 |

|          | :               | We know that $I_C = \beta I_B + (1 + \beta)$ . $I_{CO}$ , where $I_{CO}$ is the leakage current. |                    |

|          |                 | I <sub>CO</sub> is strongly dependent on temperature.                                            |                    |

|          |                 | The flow of collector current produces heat within the transistor.                               |                    |

|          |                 | This raises the transistor temperature.                                                          |                    |

|          |                 | If no stabilization is done, I <sub>co</sub> further increases.                                  |                    |

|          |                 | If $I_{CO}$ increases, $I_C$ increases by (1+ $\beta$ ). $I_{CO}$                                |                    |

|          |                 | The increased $I_{C}$ will raise the temperature of the transistor which in-turn will increase   |                    |

|          |                 | the $I_{CO}$ . This effect is cumulative and in a fraction of a second Ic becomes so large       |                    |

|          |                 | causing transistor to burn up. This self-destruction of an unstabilized transistor is            |                    |

|          |                 | known as Thermal Runaway.                                                                        |                    |

|          |                 | Power<br>dissipation t<br>Ict                                                                    |                    |

|          |                 | Thermal Runaway can be avoided :                                                                 | 1M                 |

|          |                 | 1. By keeping $I_{C}$ constant. This is done by causing $I_{B}$ to decrease automatically with   |                    |

|          |                 | temperature increase.                                                                            |                    |

|          |                 | 2. By using heat sink.                                                                           |                    |

|          |                 |                                                                                                  |                    |

Subject Name: Electronic Devices & Circuits Model Answer

## **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

## **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

Subject Name: Electronic Devices & Circuits Model Answer

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

| In above figure, transistor is connected in series with                                                                                                                   |                                        |                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------|

| as a series regulator.                                                                                                                                                    | load, therefore the circuit is known   | 2M                 |

| The transistor behaves as variable resistance whose whose whose whose whose whose whose current.                                                                          | alue is determined by the amount of    |                    |

| $V_L = V_Z - V_{BE}$                                                                                                                                                      |                                        |                    |

| (OR)                                                                                                                                                                      |                                        |                    |

| $V_{BE} = V_Z - V_L$ Equation 1                                                                                                                                           |                                        |                    |

| Suppose that value of load resistance is increased decreases and load voltage ( $V_L$ ) tend to increase. From will decrease $V_{BE}$ because $V_Z$ value is fixed.       | -                                      |                    |

| As a result of this, forward bias of the transistor i conduction. This increases $V_{CE}$ of transistor which wi for the increase in the value of load resistance so that | Il slightly decrease the input current |                    |

| If the output voltage decreases, then exactly opposi voltage is regulated.                                                                                                | te action will take place and output   |                    |

| The output of a transistor series regulator is approxim<br>regulator can also be used for larger load currents.                                                           | ately equal to zener voltage (Vz) This |                    |

|                                                                                                                                                                           |                                        |                    |

| Q.     Sub     Answers       No     Q.                                                                                                                                    |                                        | Marking<br>Scheme  |

| . N.                                                                                                                                                                      |                                        |                    |

| 3 Attempt any FOUR:                                                                                                                                                       |                                        | 16- Total<br>Marks |

| a Compare CB, CE and CC configuration on the basis of,                                                                                                                    |                                        | 4M                 |

| (i) Input Impedance (Ri)                                                                                                                                                  |                                        |                    |

| (ii) Output Impedance (Ro)                                                                                                                                                |                                        |                    |

| (iii) Voltage gain (Av)                                                                                                                                                   |                                        |                    |

| (iv) Current gain (Ai)                                                                                                                                                    |                                        |                    |

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

| •   | Parameter                                                                                                                                                                                                               | Common Base                                                                                                                                                              | Common Emitter                                                                            | Common Collector                                          | 1M each               |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------|

| •   | Input Impedance                                                                                                                                                                                                         | Low (50 Ohm)                                                                                                                                                             | Moderate (1 KOhm)                                                                         | High (300 KOhm)                                           | (numerical            |

|     | Output Impedance                                                                                                                                                                                                        | High (1 M Ohm)                                                                                                                                                           | Moderate (50 K)                                                                           | Low (300 Ohm)                                             | values for parameters |

|     | Voltage Gain                                                                                                                                                                                                            | High                                                                                                                                                                     | Higher than CB                                                                            | Less than Unity                                           | are optiona           |

|     | Current Gain                                                                                                                                                                                                            | Less than Unity                                                                                                                                                          | High                                                                                      | Very High                                                 |                       |

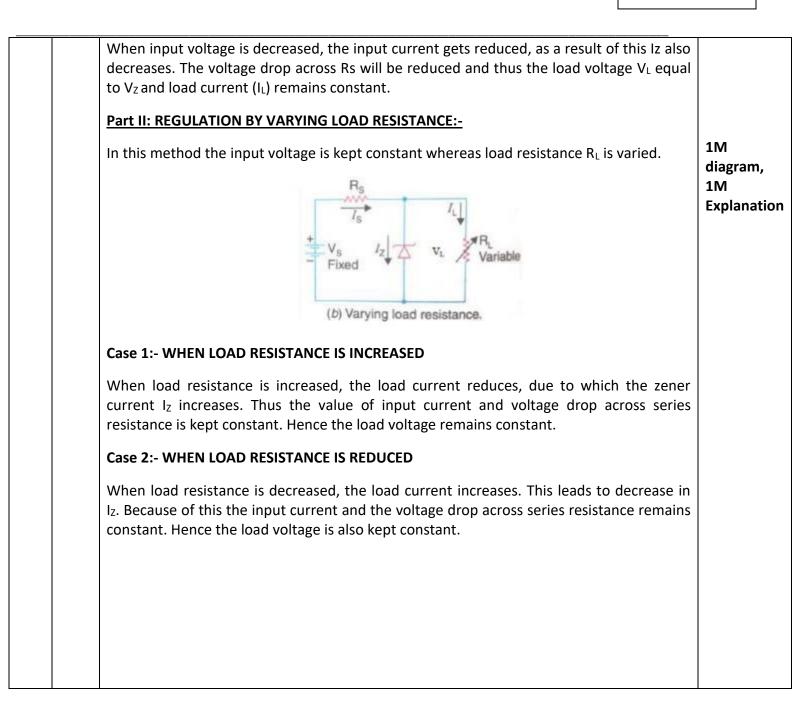

| b   | Draw the circuit diag                                                                                                                                                                                                   | ram of self-bias met                                                                                                                                                     | hod of JFET and describe                                                                  | e its working.                                            | 4M                    |

| Ans | Self Biasing Method:-                                                                                                                                                                                                   |                                                                                                                                                                          |                                                                                           |                                                           | Diagram-2             |

| :   | The self-bias c                                                                                                                                                                                                         | onfiguration for FET(d                                                                                                                                                   | c equivalent circuit) is as sh                                                            | own in fig. This                                          | Working-2             |

|     | configuration eliminate                                                                                                                                                                                                 | -                                                                                                                                                                        |                                                                                           | U U                                                       |                       |

|     | -                                                                                                                                                                                                                       |                                                                                                                                                                          |                                                                                           |                                                           |                       |

|     |                                                                                                                                                                                                                         |                                                                                                                                                                          | V <sub>DD</sub>                                                                           |                                                           |                       |

|     |                                                                                                                                                                                                                         |                                                                                                                                                                          | l                                                                                         |                                                           |                       |

|     |                                                                                                                                                                                                                         |                                                                                                                                                                          |                                                                                           |                                                           |                       |

|     |                                                                                                                                                                                                                         |                                                                                                                                                                          | ID                                                                                        |                                                           |                       |

|     |                                                                                                                                                                                                                         |                                                                                                                                                                          |                                                                                           |                                                           |                       |

|     |                                                                                                                                                                                                                         |                                                                                                                                                                          | →                                                                                         |                                                           |                       |

|     |                                                                                                                                                                                                                         | RG                                                                                                                                                                       | Is↓                                                                                       |                                                           |                       |

|     |                                                                                                                                                                                                                         | RG                                                                                                                                                                       | →<br>Is<br>↓<br>RS                                                                        |                                                           |                       |

|     |                                                                                                                                                                                                                         | RG                                                                                                                                                                       |                                                                                           |                                                           |                       |

|     |                                                                                                                                                                                                                         |                                                                                                                                                                          | RS<br>T                                                                                   |                                                           |                       |

|     | -                                                                                                                                                                                                                       | such that the gate sou                                                                                                                                                   | rce junction is always reve                                                               |                                                           |                       |

|     | requires a negative V <sub>GS</sub>                                                                                                                                                                                     | such that the gate sou                                                                                                                                                   | RS<br>T                                                                                   |                                                           |                       |

|     | requires a negative V <sub>GS</sub><br>above –                                                                                                                                                                          | such that the gate sou<br>for n channel JFET. Th                                                                                                                         | rce junction is always reve<br>is can be achieved using th                                | e self bias arrangement as                                |                       |

|     | requires a negative V <sub>GS</sub><br>above –<br>The resistor F                                                                                                                                                        | such that the gate sou<br>for n channel JFET. Th<br>R <sub>G</sub> does not affect the P                                                                                 | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative V <sub>GS</sub><br>above –<br>The resistor F<br>it and therefore gate re                                                                                                                            | such that the gate sou<br>for n channel JFET. Th<br>R <sub>G</sub> does not affect the P                                                                                 | rce junction is always reve<br>is can be achieved using th                                | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative V <sub>GS</sub><br>above –<br>The resistor F<br>it and therefore gate re<br>amplifier application.                                                                                                  | such that the gate sou<br>for n channel JFET. Th<br>R <sub>G</sub> does not affect the R<br>emains at OV. R <sub>G</sub> is nece                                         | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative V <sub>GS</sub><br>above –<br>The resistor F<br>it and therefore gate re<br>amplifier application.<br>From above diagram I <sub>S</sub>                                                             | such that the gate sou<br>for n channel JFET. Th<br>$R_G$ does not affect the R<br>emains at OV. $R_G$ is nece<br>= $I_D \& V_G = 0$                                     | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative V <sub>GS</sub><br>above –<br>The resistor F<br>it and therefore gate re<br>amplifier application.                                                                                                  | such that the gate sou<br>for n channel JFET. Th<br>$R_G$ does not affect the R<br>emains at OV. $R_G$ is nece<br>= $I_D \& V_G = 0$                                     | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative V <sub>GS</sub><br>above –<br>The resistor F<br>it and therefore gate re<br>amplifier application.<br>From above diagram I <sub>S</sub><br>∴ voltage across R <sub>S</sub> = V                      | such that the gate sou<br>for n channel JFET. Th<br>$R_G$ does not affect the R<br>emains at OV. $R_G$ is nece<br>= $I_D \& V_G = 0$                                     | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative V <sub>GS</sub><br>above –<br>The resistor F<br>it and therefore gate re<br>amplifier application.<br>From above diagram I <sub>S</sub>                                                             | such that the gate sou<br>for n channel JFET. Th<br>$R_G$ does not affect the R<br>emains at OV. $R_G$ is nece<br>= $I_D \& V_G = 0$                                     | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative $V_{GS}$<br>above –<br>The resistor F<br>it and therefore gate re<br>amplifier application.<br>From above diagram Is<br>$\therefore$ voltage across $R_S = V$<br>$\therefore V_S = I_D \cdot R_S$ . | such that the gate sou<br>for n channel JFET. Th<br>$R_G$ does not affect the R<br>emains at OV. $R_G$ is nece<br>= $I_D \& V_G = 0$                                     | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

|     | requires a negative $V_{GS}$<br>above –<br>The resistor F<br>it and therefore gate re<br>amplifier application.<br>From above diagram Is<br>$\therefore$ voltage across $R_S = V$<br>$\therefore V_S = I_D \cdot R_S$ . | such that the gate sou<br>for n channel JFET. Th<br>$R_G$ does not affect the R<br>emains at OV. $R_G$ is nece<br>$= I_D \& V_G = 0$<br>$r_{RS} = I_S . R_S = I_D . R_S$ | rce junction is always reve<br>is can be achieved using th<br>bias because it has essenti | e self bias arrangement as<br>ally no voltage drop across |                       |

## **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

Subject Code: 17319

V<sub>GS</sub> = - I<sub>D</sub>. R<sub>S</sub> From Shockley's equation the drain current is:  $I_{\rm D} = I_{\rm DSS} \left[ 1 - \frac{V_{GS}}{V_{GS(off)}} \right]^2$ Substitute the value of  $V_{GS}$  = -  $I_D$  .  $R_S$  $I_{\rm D} = I_{\rm DSS} \left[ 1 - \frac{I_D R_S}{V_{GS(off)}} \right]^2$  $I_{\rm D} = I_{\rm DSS} \left[ 1 + \frac{I_D R_S}{V_{GS(off)}} \right]^2$ The drain voltage with respect to ground is determined as follows - $V_D = V_{DD} - I_D R_D$  $V_s = I_D R_s$ The drain to source voltage is - $V_{DS} = V_D - V_S$ .  $V_{DS}$ = ( $V_{DD}$  -  $I_D R_D$ ) -  $I_D R_S$  $V_{DS} = V_{DD} - I_D R_D - I_D R_S$ Q point of self Bias circuit is located as - $V_{DS} = V_{DD} - I_D (R_D + R_S)$  $V_{GS}$  = -  $I_DR_S$  $I_{\rm D} = I_{\rm DS} \left[ 1 + \frac{I_D R_S}{V_{GS(off)}} \right]^2$  $V_{DS} = V_{DD} - I_D R_D - I_D R_S$

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

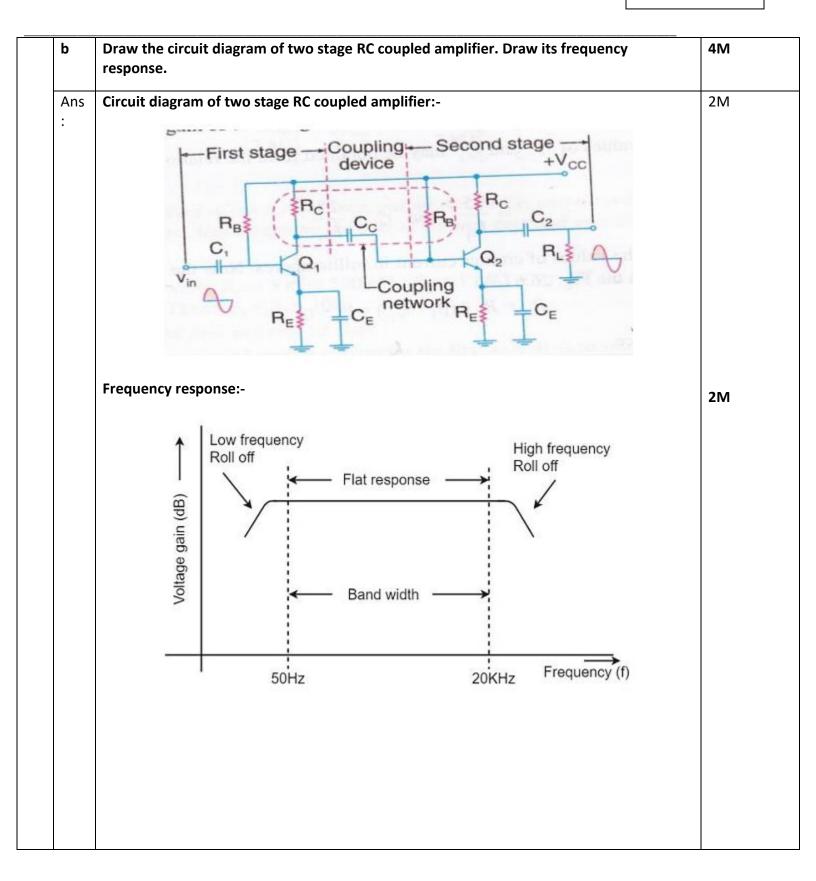

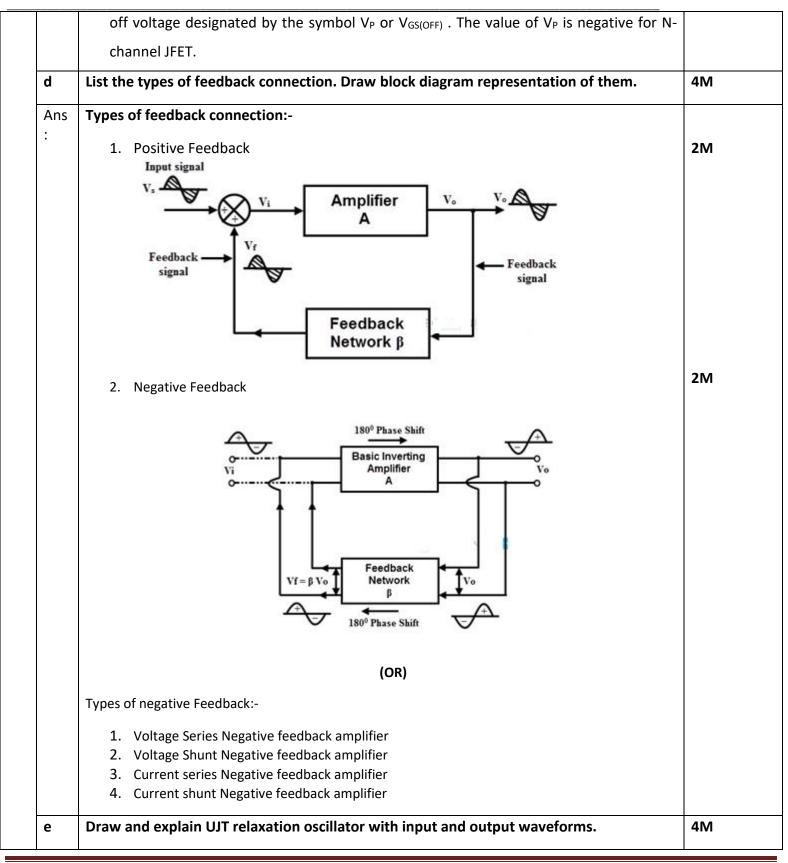

| 2   | Draw the circuit diagram of double tuned amplifier and describe its working.                                                                                                              | 4M         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Ans | Circuit diagram:-                                                                                                                                                                         | Diagram-2M |

|     | Vss                                                                                                                                                                                       | Working-2M |

|     |                                                                                                                                                                                           |            |

|     |                                                                                                                                                                                           |            |

|     | $R1 \stackrel{\texttt{L}}{=} \begin{array}{c} -c_1 & c_1 \\ \hline \\ $                                   |            |

|     |                                                                                                                                                                                           |            |

|     |                                                                                                                                                                                           |            |

|     | Vin (V) R2 RE CE CE                                                                                                                                                                       |            |

|     |                                                                                                                                                                                           |            |

|     | Working:-                                                                                                                                                                                 |            |

|     | working                                                                                                                                                                                   |            |

|     | When a signal containing many frequencies is applied at the input, the frequency                                                                                                          |            |

|     | corresponding to the resonant freq. of tuned circuit comprising of $C_1 \& L_1$ is selected, and                                                                                          |            |

|     | other frequencies are rejected. The tuned circuit offers very high impedance to this signal                                                                                               |            |

|     | frequency. Amplified output appears across the tuned circuit $L_1 C_1$ . The output from this tuned circuit is transferred to the second tuned circuit $L_2 C_2$ through mutual induction |            |

|     | .Frequency response of doubled tuned circuit depends upon the magnetic coupling of $L_1$ &                                                                                                |            |

|     | $L_2$ .                                                                                                                                                                                   |            |

|     |                                                                                                                                                                                           |            |

|     | A frequency response curve of a typical doubled tuned circuit at different coupling condition is shown –                                                                                  |            |

|     |                                                                                                                                                                                           |            |

|     | Gain 🔺 🔹 Loose coupling                                                                                                                                                                   |            |

|     |                                                                                                                                                                                           |            |

|     | Tight coupling                                                                                                                                                                            |            |

|     |                                                                                                                                                                                           |            |

|     |                                                                                                                                                                                           |            |

|     | Fr Frequency                                                                                                                                                                              |            |

|     | From above it is seen that most suitable curve is one when optimum coefficient of                                                                                                         |            |

|     | coupling exists between the tuned circuits. In this condition, the circuit is highly selective &                                                                                          |            |

|     | also provides sufficient amount of gain for a particular band of freq.                                                                                                                    |            |

|     |                                                                                                                                                                                           |            |

|     | Thus by adjusting coupling between two coils the required result can be obtained.                                                                                                         |            |

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

|          | (frequency response curve is optional. Marks may be awarded even if it is not drawn.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

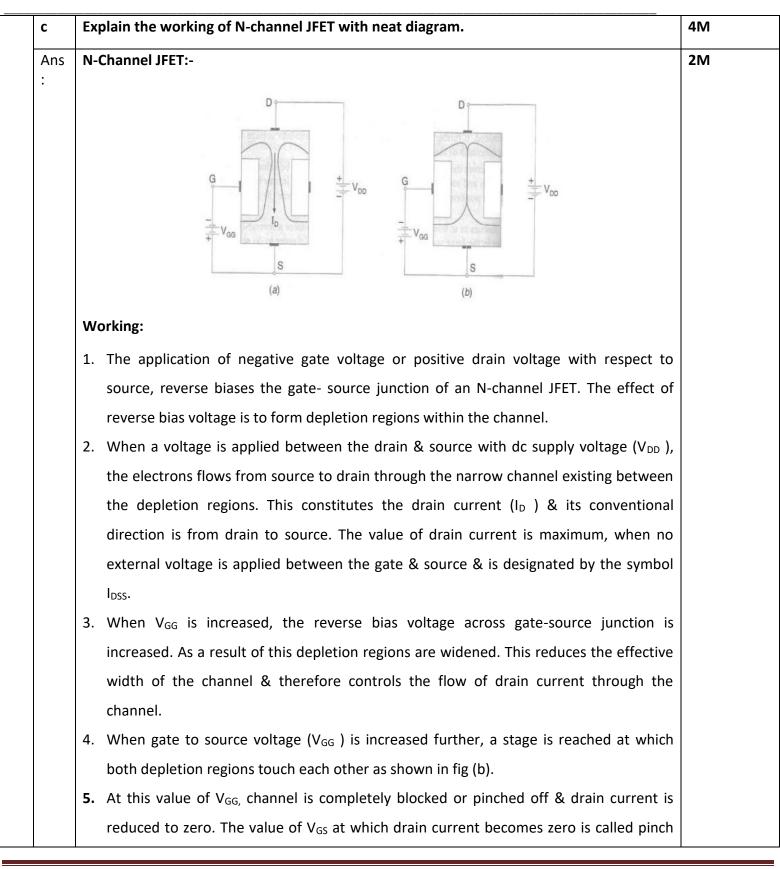

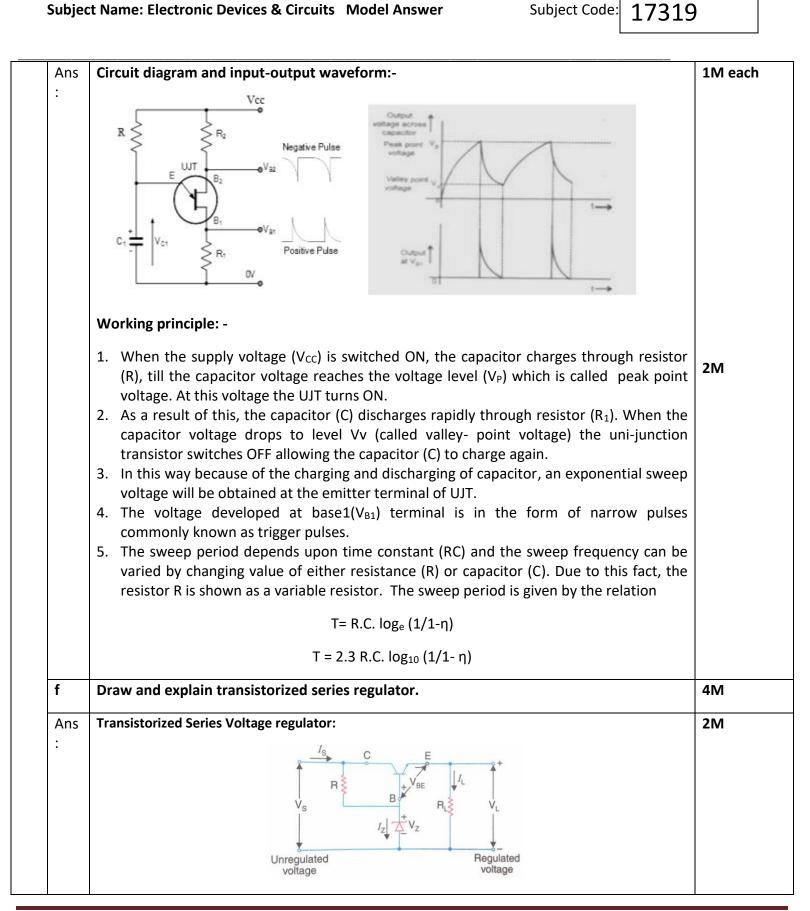

| d        | Draw pin diagram of IC 723. Give any four important features of IC 723.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4M                    |

| Ans<br>: | Pin diagram of IC 723:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin diagram<br>2M     |

|          | Current Limit 2<br>Current Sense 3<br>Inverting Input 4<br>Non Inverting Input 5<br>Vref 6<br>V-7<br>N-7<br>NC<br>NC<br>NC<br>Current Limit 2<br>T23<br>IN Frequency Compensation<br>II V+<br>II Vc<br>II Vc<br>I |                       |

|          | Important features of 723:<br>The important features of IC 723 regulator is as given below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Any four<br>features- |

|          | <ul> <li>It is small in size and less in cost.</li> <li>Positive or negative supply operation.</li> <li>Unregulated dc supply voltage at the input between9.5V and 40V</li> <li>Output voltage adjustable from 2 V to 37 V.</li> <li>Maximum load current of 150 mA</li> <li>With additional transistor used, I<sub>Lmax</sub> upto10A is available</li> <li>Internal power dissipation of 800mW</li> <li>Wide variety of applications such as series, shunt, switching and floating regulators.</li> <li>Relative simplicity with power supply can be designed.</li> <li>Low standby current gain.</li> <li>Very low temperature drift</li> <li>High ripple rejection.</li> <li>Built in fold back current limiting.</li> <li>Built in short circuit protection.</li> <li>Load and line regulations of 0.03%</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1/2 M each            |

| e        | Draw and explain transistorized crystal oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4M                    |

# **SUMMER-18 EXAMINATION**

# Subject Name: Electronic Devices & Circuits Model Answer

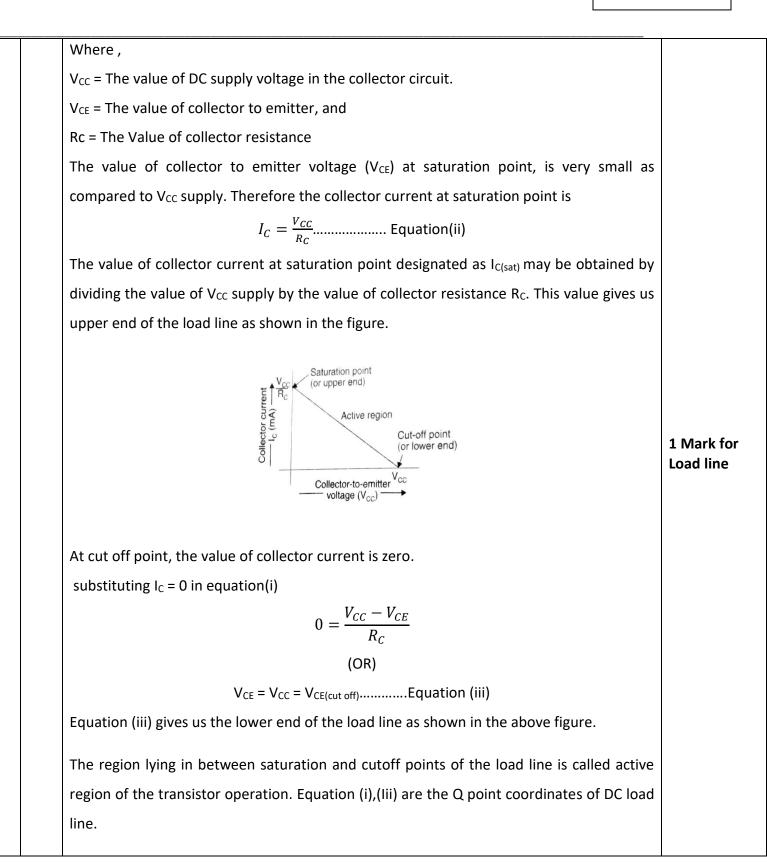

| Ans           | Circuit Diagram:                                                                                                                                                                                                                                                                                                                                                                                                    | Circuit                   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| :             | + V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                   | Diagram-2N                |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                     | Explanation<br>2M         |

|               | Working:-                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

|               | When the power is turned on, capacitor $C_1$ is charged. When this capacitor discharges, it sets up oscillations. The voltage across $L_1$ is applied to coil $L_2$ due to mutual inductance. This positive feedback causes the oscillator to produce oscillations. The frequency of oscillations in the circuit is controlled by the crystal. As the crystal is connected in the base circuit its influence on the |                           |

|               | frequency of the circuit is much more than LC circuit. The entire circuit vibrates at the natural frequency of the crystal. As the frequency of the crystal is independent of temperature, the circuit generates a constant frequency.                                                                                                                                                                              |                           |

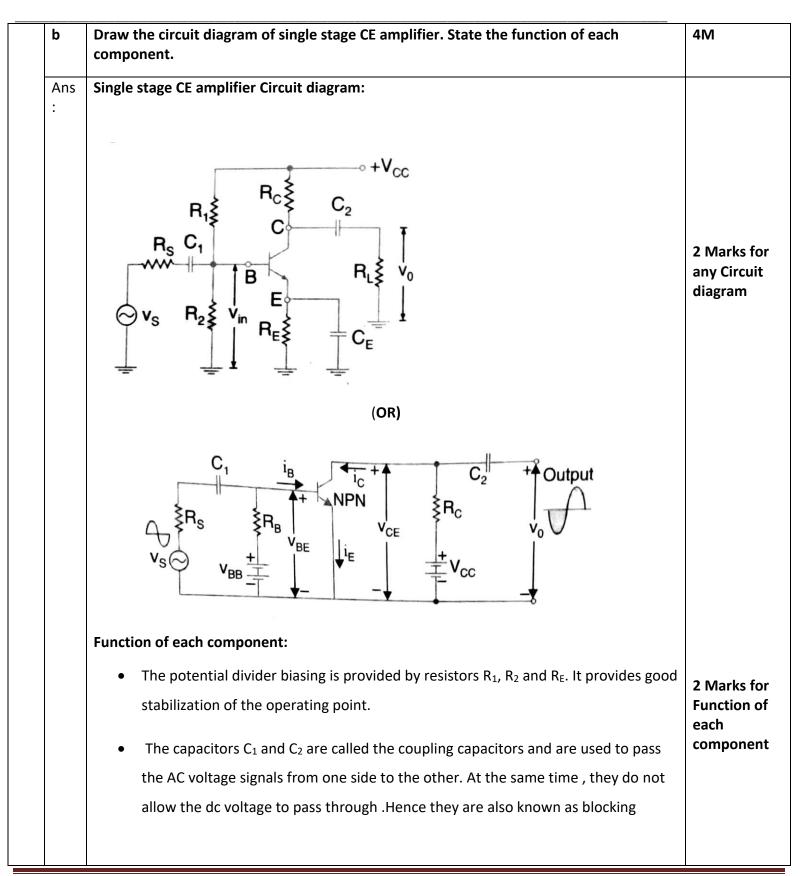

| f             | frequency of the crystal. As the frequency of the crystal is independent of temperature, the circuit                                                                                                                                                                                                                                                                                                                | 4M                        |

| f<br>Ans<br>: | frequency of the crystal. As the frequency of the crystal is independent of temperature, the circuit generates a constant frequency.                                                                                                                                                                                                                                                                                | Diagram-2N                |

| Ans           | frequency of the crystal. As the frequency of the crystal is independent of temperature, the circuit generates a constant frequency.<br>Draw and explain class-B push pull amplifier.<br>$ \begin{array}{c}                                     $                                                                                                                                                                   | Diagram-2N<br>Explanatior |

| Ans           | frequency of the crystal. As the frequency of the crystal is independent of temperature, the circuit generates a constant frequency.<br>Draw and explain class-B push pull amplifier.  T2 Vin                                                                                                                                                                                   | Diagram-2N<br>Explanation |

# **SUMMER-18 EXAMINATION**

Subject Name: Electronic Devices & Circuits Model Answer

|          |                 | negative. Therefore Q <sub>1</sub> conducts (ON) and Q <sub>2</sub> is OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |

|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

|          |                 | When negative half cycle is applied across input, the base of $Q_1$ becomes negative and the base of $Q_2$ is positive. Therefore $Q_1$ is OFF and $Q_2$ conducts. only $i_{c2}$ flows and $i_{c1} = 0$ . A negative sinusoidal voltage will appear across load.<br>Thus at any instant only one transistor will conduct. When $Q_1$ conducts, only $i_{c1}$ flows and $i_{c2} = 0$ . A                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |

| 0        | Sub             | positive sinusoidal voltage will appear across load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Marking                                               |