## A TREMINIST OF THE STATE OF THE

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

### (ISO/IEC - 27001 - 2013 Certified) WINTER— 17 EXAMINATION

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.     | Su | Answer                                                                     | Marki            |

|--------|----|----------------------------------------------------------------------------|------------------|

| No     | b  |                                                                            | ng<br>Schem      |

| •      | Q. |                                                                            | e                |

| 1<br>A | a  | Sketch Symbol and label terminals of i) PNP Transistor ii) Photodiode    B | 1 mark<br>each   |

|        |    | i) PNP Transistor ii) Photodiode                                           |                  |

|        | В  | State input and output terminals in CB and CE configuration of BJT.        |                  |

|        |    | CB – Input terminal – Emitter – base                                       | 1 mark<br>for CB |

|        |    | Output terminal – Collector- base.                                         | and 1<br>Mark    |

|        |    | CE – Input terminal – Base –Emitter                                        | for CE           |

|        |    | Output terminal – Collector – Emitter.                                     |                  |

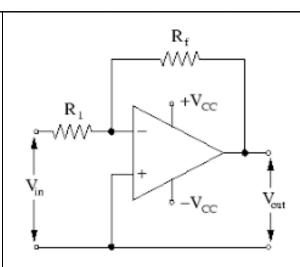

|        | c  | Draw the circuit diagram of an op-amp as inverting amplifier.              |                  |

|        |    |                                                                            |                  |

|        |    |                                                                            |                  |

d

e

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

#### (ISO/IEC - 27001 - 2013 Certified)

WINTER- 17 EXAMINATION

Subject Name: BEM <u>Model Answer</u>

Subject Code: 17302

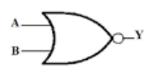

Draw the symbol of NOR gate. Give its truth table.

| in | puts | output |

|----|------|--------|

| Α  | В    | Y      |

| 0  | 0    | 1      |

| 0  | 1    | 0      |

| 1  | 0    | 0      |

| 1  | 1    | 0      |

Symbo 1 – 1 Mark

Marks

TT - 1 Mark

- What are the advantages of Flexible Manufacturing system (FMS)? (any four)

- 1. Large variety of same products

- 2. Profitable investment.

- 3. Requires limited inventory.

- 4. Low labor cost.

- 5. Flexible system.

- 6. Speedy production.

- 7. Improve product quality.

f List different types of flip-flops.

- S R Flip-flop

- JK Flip-flop

- T- Flip-flop

1/2 Mark to each point

Mark to each FF

## (Autonomous) (ISO/IEC - 27001 - 2013 Certified)

WINTER- 17 EXAMINATION

|   |   | - D- Flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |

|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|   | g | List the different types of oscillators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1/2                     |

|   |   | - RC Phase shift oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mark<br>to each         |

|   |   | - Hartly Oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | oscillat<br>or          |

|   |   | - Colpitt's Oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Oi                      |

|   |   | - Crystal Oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |

|   | h | Define intrinsic and extrinsic semiconductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |

|   |   | Intrinsic – Semiconductor in pure form is called as intrinsic semiconductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 Mark                  |

|   |   | Extrinsic – Semiconductor with added impurity is called as extrinsic semiconductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | to each                 |

| 1 | a | Define line regulation and load regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| В |   | 1. Line Regulation Line regulation is a measure of the ability of the power supply to maintain its output voltage given changes in the input line voltage. Line regulation is expressed as percent of change in the output voltage relative to the change in the input line voltage. $Line\ regulation = \left(\frac{\Delta V_{OUT}}{\Delta V_{IN}}\right) \times 100\%$ $\Delta \ means\ "a\ change\ in"$ 2. Load Regulation Load regulation is a measure of the ability of an output channel to remain constant given changes in the load. $Load\ regulation = \left(\frac{V_{NL} - V_{FL}}{V_{FL}}\right) \times 100\%$ | 2<br>Mark<br>to<br>each |

|   |   | <ul> <li>Where:</li> <li>V<sub>NL</sub> = the no-load output voltage</li> <li>V<sub>RL</sub> = the full-load output voltage</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |

|   |   | What is thermal runaway? How it is avoided?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

(Autonomous)

#### (ISO/IEC - 27001 - 2013 Certified)

WINTER-17 EXAMINATION

Subject Name: BEM Model Answer Subject Code: 17302

b What is the thermal runaway?

**Thermal runaway** occurs in situations where an increase in temperature changes the conditions in a way that causes a further increase in temperature, often leading to a destructive result. It is a kind of uncontrolled positive feedback.

#### What is thermal runaway of a transistor?

Thermal runaway. The problem with increasing temperature causing increasing collector current is that more current increase the power dissipated by the transistor which, in turn, increases its temperature. This self-reinforcing cycle is known as thermal run away, which may destroy the transistor.

Runa way explai n

Marks

How it is avoided?

This is achieved by selecting a sheet of metal called the **HEAT SINK** which increases the area of contact With the atmosphere.

Avoid ed – 1 Mark

Marks

each

point

### c State selection criteria for transducer. (any 4)

- **Operating Principle:** The transducers are selected on the basis of operating principle it may be resistive, inductive, capacitive, optical etc.

- **Operating range:** The range of transducer should be appropriate for measurement to get a good resolution.

- **Accuracy**: The accuracy should be as high as possible or as per the measurement.

- **Range:** The transducer can give good result within its specified range, so select transducer as per the operating range.

• **Sensitivity**: The transducer should be more sensitive to produce the output or sensitivity should be as per requirement.

Loading effect: The transducer's input impedance should be high and output impedance should be low to avoid loading effect.

• Errors: The error produced by the transducer should be low as possible.

• Environmental compatibility: The transducer should maintain input and output characteristic for the selected environmental condition.

ut

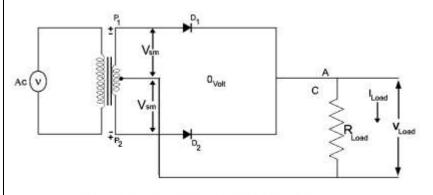

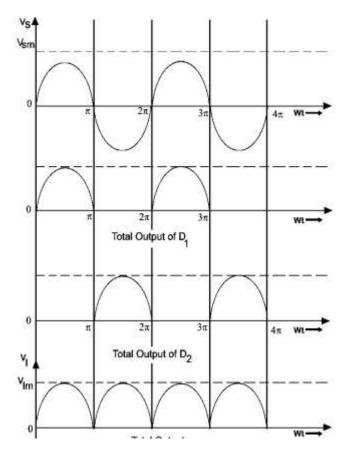

# Describe the working of center tapped full wave rectifier with circuit diagram and waveform.

**CENTRE - TAP FULL- WAVE RECTIFIER CIRCUIT**

Ckt – 1 Mark

W/F -

Page 4 of 26

2

a

(Autonomous)

### (ISO/IEC - 27001 - 2013 Certified) WINTER— 17 EXAMINATION

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

#### Working of Centre-Tap Full Wave Rectifier

Mark

As shown in the figure, an ac input is applied to the primary coils of the transformer. This input makes the secondary ends P1 and P2 become positive and negative alternately. For the positive half of the ac signal, the secondary point D1 is positive, GND point will have zero volt and P2 will be negative. At this instant diode D1 will be forward biased and diode D2 will be reverse biased. As explained in the Theory Behind P-N Junction and Characteristics of P-N Junction Diode, the diode D1 will conduct and D2 will not conduct during the positive half cycle. Thus the current flow will be in the direction P1-D1-C-A-B-GND. Thus, the positive half cycle appears across the load resistance RLOAD.

Explai n- 2 Marks

During the negative half cycle, the secondary ends P1 becomes negative and P2 becomes positive. At this instant, the diode D1 will be negative and D2 will be positive with the zero reference point being the ground, GND. Thus, the diode D2 will be forward biased and D1 will be reverse biased. The diode D2 will conduct and D1 will not conduct during the negative half cycle. The current flow will be in the direction P2-D2-C-A-B-GND. Thus, the negative half cycle appears across the load resistance RLOAD.

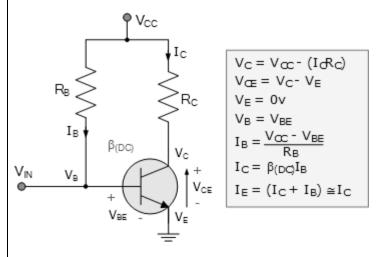

List different biasing methods of BJT. Draw the circuit diagram of fixed bias circuit method.

- Base Bias (Fixed Bias)

- Voltage divider bias

(Autonomous)

### (ISO/IEC - 27001 - 2013 Certified) WINTER— 17 EXAMINATION

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

- Emitter bias

- Collector feedback bias

#### circuit diagram of fixed bias circuit method.

List – 1 Mark

Ckt – 3 Marks

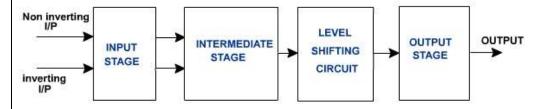

### Draw and explain block diagram of op-amp.

#### The Input Stage

c

The input stage consisting of "Dual Input Balanced Output Differential Amplifier"

This stage Determines the Input Impedance of Operational Amplifier, having two inputs Inverting and

Non-Inverting.

In this stage Differential amplifier with a constant current source is used in order to Increase the CMRR (common mode rejection ratio).

#### The Intermediate Stage

This stage also posses Two inputs but having only One Output. It is usually another Differential amplifier, which is driven by the preceding Output. This stage is commonly used to Increase the gain of amplifier. In the quiescent condition some dc error voltage may appears on the Output of This stage.

### The Level Shifting stage

This stage is usually an Emitter Follower circuit in order to shift the error dc Level of preceding stage.

This stage eliminates the chance of signal distortions.

#### The Output Stage

It is final Stage of an Operational amplifier; it is usually a complementary symmetry push pull Amplifier.

$\begin{array}{l} Diagra\\ m-2\\ Marks \end{array}$

Explai n- 2 Marks

d

e

#### MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous)

#### (ISO/IEC - 27001 - 2013 Certified) WINTER-17 EXAMINATION

Subject Name: **Model Answer** Subject Code: 17302 **BEM**

This Stage Increases the Output voltage swing and the current delivering capabilities. It also essential for providing low output Impedance.

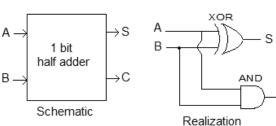

#### Explain half adder with its logical circuit diagram and truth table

Truth table

Half adder is a combinational arithmetic circuit that adds two numbers and produces a sum bit (S) and carry bit (C) as the output. If A and B are the input bits, then sum bit (S) is the X-OR of A and B and the carry bit (C) will be the AND of A and B. From this it is clear that a half adder circuit can be easily constructed using one X-OR gate and one AND gate. Half adder is the simplest of all adder circuit, but it has a major disadvantage. The half adder can add only two input bits (A and B) and has nothing to do with the carry if there is any in the input. So if the input to a half adder have a carry, then it will be neglected it and adds only the A and B bits. That means the binary addition process is not complete and that's why it is called a half adder. The truth table, schematic representation and XOR//AND realization of a half adder are shown in the figure.

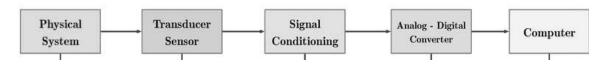

### Draw and explain single channel Data Acquisition System (DAS)

### Digital Data Acquisition System

**Physical System-** the system which parameters are to be monitored / recorded.

Transducer Sensor – The second stage is a transducer which converts one form of energy into another. Like temperature sensor, humidity sensor, pressure sensors etc.

**Signal conditioning** – this block is used to convert the signal coming from transducer into proper voltage/current level which is required by analog to digital converter.

Analog-Digital Converter – this block converts the analog signals into digital. It is necessary to store/process the digital data in computer system.

Computer – this is a system which processes the digital data, which stores the result and displays the result on connected display.

Mark

Ckt-

TT- 1 Mark

Explai n- 2 Marks

Diagra m-2Marks

Explai n- 2 Marks

# MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

|   | f | Explain briefly Advance Vehicle Control System (AVCS)                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |   | Advanced Vehicle Control Systems (AVCS or AVEC) is part of the "Smart Highway" initiative (also known as Intelligent Vehicle Highway Systems (IVHS) or Intelligent Transportation Systems (ITS) now receiving considerable study worldwide.                                                                                                                                                                                                                                         | 4<br>Marks |

|   |   | AVCS is A set of technologies designed to enhance driver control and vehicle safety. This ranges up to Automated Highway Systems (AHS), where the driver cedes all control to the system.                                                                                                                                                                                                                                                                                           |            |

|   |   | The potential benefits of automating the guidance of automobiles are extensive especially with regard to better utilization of highway space and safety.                                                                                                                                                                                                                                                                                                                            |            |

|   |   | we could replace safety related driver functions with technology, an automated system could eventually be very substantially safer than the existing system in that we could bring technology to bear directly on a problem that is now virtually completely driver controlled. Vehicle automation could therefore easily be the greatest public health advance of the twenty-first century.                                                                                        |            |

|   |   | A vehicle guidance system necessarily have to be highly sophisticated and presumably involve substantial electronics, computers, and software                                                                                                                                                                                                                                                                                                                                       |            |

|   |   | Highways automation systems could have "machine readable" signs, marks, or electronic signals to aid in guidance and supplement any imagery analysis system.                                                                                                                                                                                                                                                                                                                        |            |

| 3 |   | Attempt any four                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16         |

|   | a | Characteristics of zener diode with circuit diagram                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|   |   | There are two types of Zener charectrestics  I) Forward Characteristics II) Reverse characteristics Forward Characteristics:- Figure 1.a shows the circuit arrengment for forward characteristics of zener diode. When forward voltage is applied the depletion region starts decreasing and after knee point voltage current start to flow. This is a non linear and same as forward characteristics of normal pn junction diode characteristics.(shown in fig.1.c First Quadrent) | 01         |

|   |   | Current limiting resistor  Fig 1.a  Fig 1.b                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01         |

## (Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

|   | increases<br>diode wil | voltage across zener diode is inc<br>l become constant, hence zener d<br>n which is called as zener break | ode is reverse biased as shon in figureased and after zener breakdown liode acts as a voltage regulator. Zodown. The revers characteristics is of Zener diode | voltage across zener ener diode has a sharp | (with expla |

|---|------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------|

|   |                        | Specified 5                                                                                               | Forward<br>characteristic<br>Voltage                                                                                                                          |                                             |             |

| b | Comparis               | Reverse breakdown son of Astable and Bistable multi                                                       | vibrator.                                                                                                                                                     |                                             | 01 *4       |

|   | Sr.No.                 | Astable M.V.                                                                                              | Bistable M.V.                                                                                                                                                 |                                             | =           |

|   | 01                     | No stable states are present.                                                                             | Both states are stable.                                                                                                                                       |                                             | 04          |

|   | 02                     | No external trigger pulse is required to change states.                                                   | Two external trigger pulses are required to change the states                                                                                                 |                                             |             |

|   | 03                     | Both states are temporary states having same time duration.                                               | States are stable and width of state will depend upon external trigger pules.                                                                                 |                                             |             |

|   | 04                     | e.g. dancing light system                                                                                 | e.g. on/off/switch, Schmitt trigger ckt.                                                                                                                      |                                             |             |

|   | Any other              | r suitable and relevant point may                                                                         | be consider.                                                                                                                                                  | 1                                           |             |

| С |                        | ing counter circuit oit ring counter 4 flip flops are re                                                  | quired.                                                                                                                                                       |                                             |             |

|   |                        |                                                                                                           |                                                                                                                                                               |                                             | 04          |

### (Autonomous) (ISO/IEC - 27001 - 2013 Certified) **WINTER-17 EXAMINATION**

|   | 4-bit Parallel Data Output                                                                                                                                                                                                                      |             |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|   | Preset to Loop  D Q D Q D Q D Q D Q D C C C C C C C C C                                                                                                                                                                                         |             |

| d | Applications of Digital to Analog convertor (DAC)                                                                                                                                                                                               | Any<br>four |

|   | DACs are used in Computer Printers.                                                                                                                                                                                                             | 01*4        |

|   | DACs are used in Digital Motor Control                                                                                                                                                                                                          | =04         |

|   | DACs are used in Sound equipments (e.g. CD/MP3 Players)                                                                                                                                                                                         | -04         |

|   | DACs Function Generator/Oscilloscopes                                                                                                                                                                                                           |             |

|   | DACs are used in Digital Audio                                                                                                                                                                                                                  |             |

|   | Any other suitable and relevant application may be considered                                                                                                                                                                                   |             |

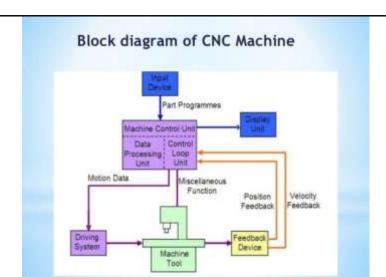

| e | Block diagram of CNC machine and Function of Each block                                                                                                                                                                                         |             |

|   | i) Input Devices: These are the devices which are used to input the part program in the CNC machine. There are three commonly used input devices and these are punch tape reader, magnetic tape reader and computer via RS-232-C communication. |             |

|   | (ii) Machine Control Unit (MCU): It is the heart of the CNC machine. It performs all the controlling action of the CNC machine, the various functions performed by the MCU are                                                                  |             |

|   | It reads the coded instructions fed into it.                                                                                                                                                                                                    |             |

|   | It decodes the coded instruction. It implements interpolation ( linear, circular and helical ) to generate axis motion                                                                                                                          |             |

|   | It feeds the axis motion commands to the amplifier circuits for driving the axis mechanisms.                                                                                                                                                    |             |

|   | It receives the feedback signals of position and speed for each drive axis.  It implements the auxiliary control functions such as coolant or spindle on/off and tool                                                                           |             |

|   | change.                                                                                                                                                                                                                                         |             |

|   |                                                                                                                                                                                                                                                 | 02          |

|   |                                                                                                                                                                                                                                                 |             |

|   |                                                                                                                                                                                                                                                 |             |

|   |                                                                                                                                                                                                                                                 |             |

(Autonomous)

#### (ISO/IEC - 27001 - 2013 Certified)

WINTER- 17 EXAMINATION

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

- (iii) Machine Tool: A CNC machine tool always has a slide table and a spindle to control of the position and speed. The machine table is controlled in X and Y axis direction and the spindle is controlled in the Z axis direction.

- **(iv) Driving System:** The driving system of a CNC machine consists of amplifier circuits, drive motors and ball lead screw. The MCU feeds the signals (i.e. of position and speed) of each axis to the amplifier circuits. The control signals are than augmented (increased) to actuate the drive motors. And the actuated drive motors rotate the ball lead screw to position the machine table.

02

02

- (v) Feedback System: This system consists of transducers that acts like sensors. It is also called as measuring system. It contains position and speed transducers that continuously monitor the position and speed of the cutting tool located at any instant. The MCU receives the signals from these transducers and it uses the difference between the reference signals and feedback signals to generate the control signals for correcting the position and speed errors.

- (vi) Display Unit: A monitor is used to display the programs, commands and other useful data of CNC machine.

- f Multiplexer: Multiplexer is a combinational logic circuit which has many Inputs and only one Output. Any one Input is selected at a time using select Inputs.

Number of select Inputs are Depends upon number of Inputs available with Multiplexer

And it is related as  $2^N = M$

Where N= Number of Select Inputs

**M= Number of Inputs to mux**

8:1 multiplexer:-

For 8:1 mux, No.Of inputs are =8 so, select inputs are required are =3

# MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

**Subject Name: BEM**

**Model Answer**

Subject Code: 17302

|   | Inputs  8:1  MUX  S2 S1 S0  Select Lines                                                                                                                                                                      | 02 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4 | Attempt any Four  Advantages and disadvantages of Mechatronics system:-                                                                                                                                       | 16 |

|   | 1)Enhanced features and functionality 2) More user-friendly 3) Precision control 4) More efficient 5) Lower cost 6) Flexible design (reprogrammable) 7) More reliable  Any other suitable and relevant points | 02 |

|   | Disadvantages:-                                                                                                                                                                                               |    |

|   | 1) different expertise required 2) more complex safety issues 3) increase in component failures 4) increased power requirements 5) lifetimes change/vary Any other suitable and relevant points               | 02 |

| b | Comparison of Electrical and Mechanical Transducers.                                                                                                                                                          |    |

|   | Sr.No. Electrical Transducer Mechanical Transducer                                                                                                                                                            |    |

|   | 01 Converts input signal into output Converts input into output in                                                                                                                                            |    |

| 1 |                                                                                                                                                                                                               |    |

# MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

|   |                     | in electrical form                                                                                                                                                                   | mechanical form                                                                                                                                                                                                                                                                        | 01*4= |

|---|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   | 02                  | Output is directly available in electrical form                                                                                                                                      | To convert mechanical output into electrical, requires instrumentation system                                                                                                                                                                                                          | 04    |

|   | 03                  | More accurate                                                                                                                                                                        | Less accurate                                                                                                                                                                                                                                                                          |       |

|   | 04                  | Speed of response is fast                                                                                                                                                            | Speed of response is less                                                                                                                                                                                                                                                              |       |

|   | Any ot              | <br>her suitable and relevant point ma                                                                                                                                               | ny be considered                                                                                                                                                                                                                                                                       |       |

| 4 | Attemp              | ot any Four                                                                                                                                                                          |                                                                                                                                                                                                                                                                                        | 16    |

| c | a)                  | Implementation of AND gate usin                                                                                                                                                      | g NAND gates                                                                                                                                                                                                                                                                           | 02    |

|   |                     | A                                                                                                                                                                                    | <b>2</b>                                                                                                                                                                                                                                                                               |       |

|   |                     | % iinga                                                                                                                                                                              | urit ANU D Carines                                                                                                                                                                                                                                                                     |       |

|   | b)                  | Implementation of OR gate using N                                                                                                                                                    | AND gates                                                                                                                                                                                                                                                                              | 02    |

|   |                     | 2. import CH & Castes                                                                                                                                                                |                                                                                                                                                                                                                                                                                        |       |

| d | Block I units/sec   |                                                                                                                                                                                      | k diagram of a PLC shown in above Fig. It has three major                                                                                                                                                                                                                              |       |

|   | •                   | I/O (Input/Output) Modules.                                                                                                                                                          |                                                                                                                                                                                                                                                                                        |       |

|   | •                   | CPU (Central Processing Units).                                                                                                                                                      |                                                                                                                                                                                                                                                                                        |       |

|   |                     | Programmer/Monitor.                                                                                                                                                                  |                                                                                                                                                                                                                                                                                        |       |

|   | the PLC The I The o | "s CPU can read. Processor Section reads these inputs, Proutput section converts the logic level of and used to actuate various output field programmer/monitor is used to enter the | supplied by input devices/sensors to logic-level signals that rocesses the signal, and prepares the output signals. Sutput signals coming from processor section to high level devices.  The devices is program into memory and to monitor the execution is supplied by input devices. |       |

|   | signals a           | and used to actuate various output field programmer/monitor is used to enter the rogram.                                                                                             | devices.                                                                                                                                                                                                                                                                               |       |

(Autonomous)

(ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

Field Outputs Push POWER SUPPLY 0 U N CPU T P P USER DATA MEMORY MEMORY SERIAL PORT PROGRAMMING DEVICE

02

#### 1) I/O Section:-

The I/O section establish the interfacing between physical devices in the real world outside the PLC and the digital arena inside the PLC.

The input module has bank of terminals for physically connecting input devices, like push buttons, limit switches etc. to a PLC. the role of an input module is to translate signals from input devices into a form that the PLC's CPU can understand.

The Output module also has bank of terminals that physically connect output devices like solenoids, motor starters, indicating lamps etc. to a PLC. The role of an output module is to translate signals from the PLC's CPU into a form that the output device can use.

02

The tasks of the I/O section can be classified as:

- Conditioning

- Isolation

- Termination

- Indication

An electronic system for connecting I/O modules to remotely located I/O devices can be added if needed. The actual operating process under PLC Control can be thousands of feet from the CPU and its I/O modules.

#### 2) CPU Section:-

The Central Processing Unit, the brain of the system is the control portion of the PLC. It has three Subparts.

- Memory System

- Processor

- Power Supply

**Memory System:-**

(Autonomous)

#### (ISO/IEC - 27001 - 2013 Certified)

**WINTER-17 EXAMINATION**

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

The memory is the area of the CPU in which data and information is stored and retrieved. The total memory area can be subdivided into the following four Sections.

• I/O Image Memory

User Memory

Executive Memory

#### Processor:-

The processor, the heart of CPU is the computerized part of the CPU in the form of Microprocessor / Micro controller chip. It supervises all operation in the system and performs all tasks necessary to fulfill the PLC function.

- It reads the information i.e status of externally connected input devices with input module.

- It stores this information in memory for later use.

- It carries out mathematical and logic operations as specified in application program.

- After solving the user's program, it writes the result values in the memory.

- It sends data out to external devices like output module, so as to actuate field hardware.

- It performs peripheral and external device communication.

- It Performs self diagnostics.

#### Power Supply:-

The power supply provides power to memory system, processor and I/O Modules.

- It converts the higher level AC line Voltage to various operational DC values.

- for electronic circuitry.

- It filters and regulates the DC voltages to ensure proper computer operations.

#### 3) Programmer/Monitor:-

The Programmer/Monitor (PM) is a device used to communicate with the circuits of the PLC. The programming unit allows the engineer/technicians to enter the edit the program to be executed.

In its simplest form it can be hand-held device with membrane keypad for program entry, and a display device (LED or LCD) for viewing program steps of functions.

e

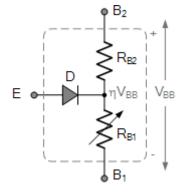

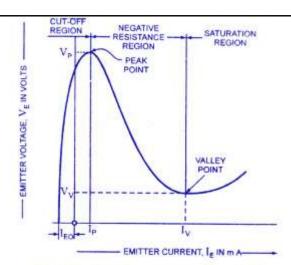

#### a) Equivalent circuit of UJT

b) I-V characteristics of UJT

02

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### WINTER- 17 EXAMINATION

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

Static Emitter-Characteristic For a UJT

The static emitter characteristic (a curve showing the relation between emitter voltage  $V_E$  and emitter current  $I_E$ ) of a  $\begin{tabular}{l} UJT$  at a given inter base voltage  $V_{BB}$  is shown in figure. From figure it is noted that for emitter potentials to the left of peak point, emitter current  $I_E$  never exceeds  $I_{Eo}$ . The current  $I_{Eo}$  corresponds very closely to the reverse leakage current  $I_{Co}$  of the conventional BJT. This region, as shown in the figure, is called the cut-off region. Once conduction is established at  $V_E = V_P$  the emitter potential  $V_E$  starts decreasing with the increase in emitter current  $I_E$ . This Corresponds exactly with the decrease in resistance  $R_B$  for increasing current  $I_E$ . This device, therefore, has a negative resistance region which is stable enough to be used with a great deal of reliability in the areas of applications listed earlier. Eventually, the valley point reaches, and any further increase in emitter current  $I_E$  places the device in the saturation region, as shown in the figure. Three other important parameters for the UJT are  $I_P$ ,  $V_V$  and  $I_V$  and are defined below:

**Peak-Point Emitter Current.**  $I_p$ . It is the emitter current at the peak point. It represents the rnimrnum current that is required to trigger the device (UJT). It is inversely proportional to the interbase voltage  $V_{BB}$ .

Valley Point Voltage  $V_V$  The valley point voltage is the emitter voltage at the valley point. The valley voltage increases with the increase in interbase voltage  $V_{BB}$ .

01

01

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### WINTER- 17 EXAMINATION

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

Valley Point Current  $I_V$  The valley point current is the emitter current at the valley point. It increases with the increase in inter-base voltage  $V_{BB}$ .

f

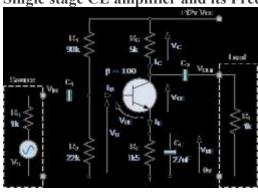

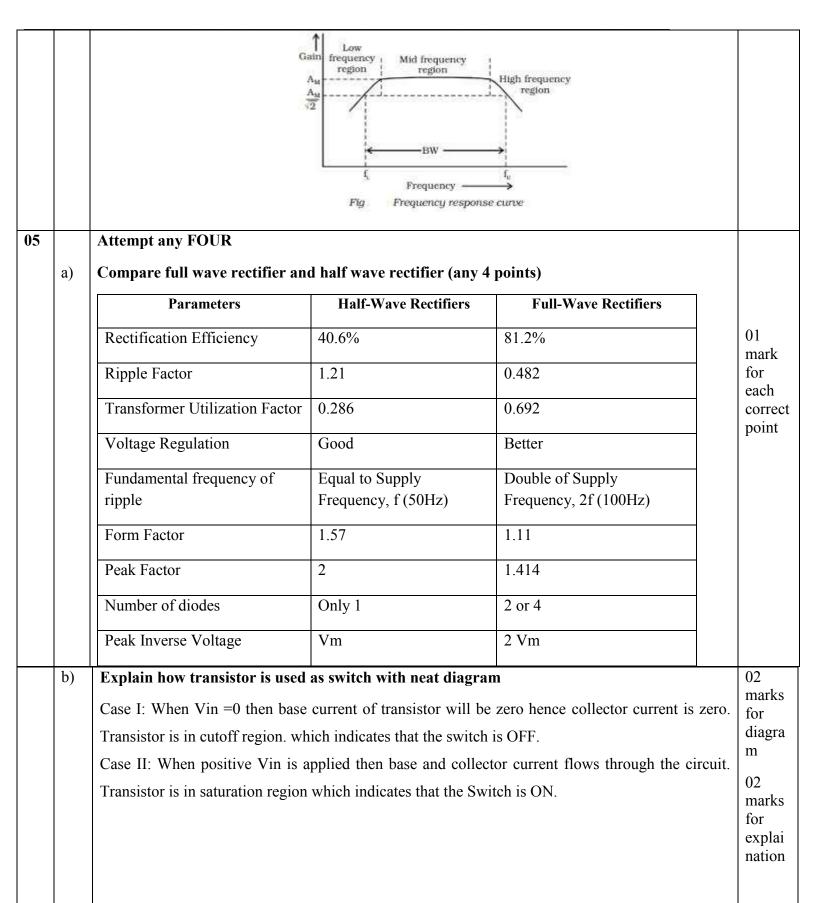

Single stage CE amplifier and its Frequency Response

02

01

The common emitter RC coupled amplifier is one of the simplest and elementary transistor amplifier that can be made. Don't expect much boom from this little circuit, the main purpose of this circuit is pre-amplification i.e to make weak signals strong enough for further processing or amplification. If designed properly, this amplifier can provide excellent signal characteristics. The circuit diagram of a single stage common emitter RC coupled amplifier using transistor is Capacitor Cin is the input DC decoupling capacitor which blocks any DC component if present in the input signal from reaching the Q1 base. If any external DC voltage reaches the base of Q1, it will alter the biasing conditions and affects the performance of the amplifier.

R1 and R2 are the biasing resistors. This network provides the transistor Q1's base with the necessary bias voltage to drive it into the active region. The region of operation where the transistor is completely switched of is called cut-off region and the region of operation where the transistor is completely switched ON (like a closed switch) is called saturation region. The region in between cut-off and saturation is called active region.

Frequency response:-

01

(Autonomous)

#### (ISO/IEC - 27001 - 2013 Certified) WINTER- 17 EXAMINATION

Subject Name: BEM

**Model Answer**

Subject Code: 17302

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

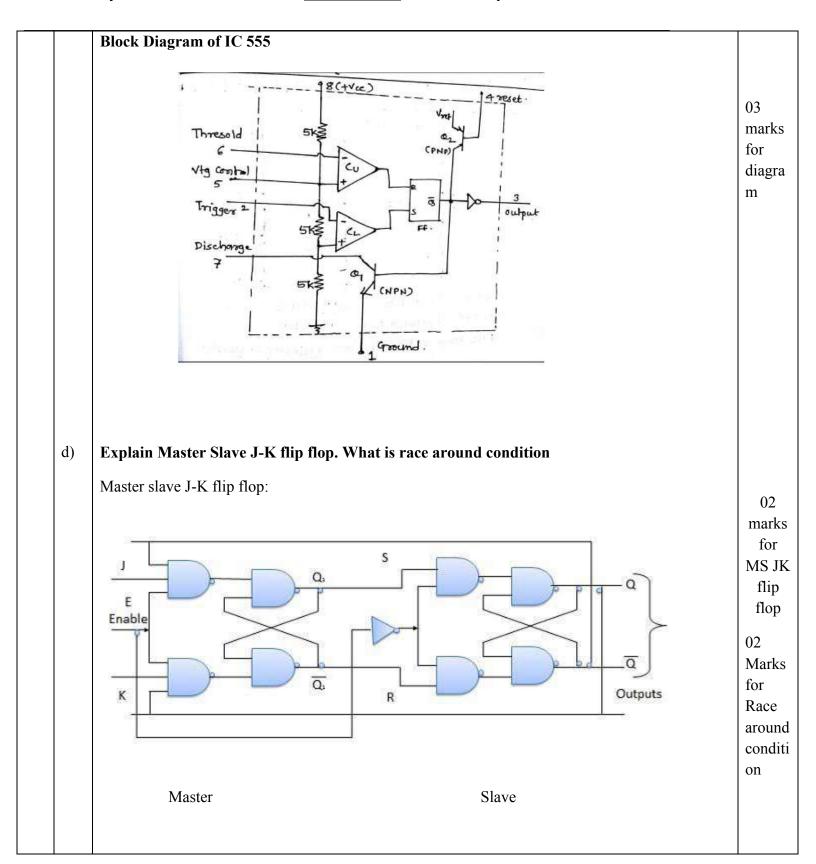

| c) | Transistor as a switch  Vin = 0 fransistor is off switch  Vin = +v Transistor is off switch  Draw the block diagram of IC 555 and label it. List its two features  Features:- |         |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|    | Adjustable duty cycle                                                                                                                                                         | 01      |

|    | 2. Output can source or sink 200mA.                                                                                                                                           | marks   |

|    | 3. Output and supply TTL compatible                                                                                                                                           | for     |

|    | 4. Temperature stability better than 0.005% per °C                                                                                                                            | feature |

|    | i. Temperature smorning setter than 0.00070 per C                                                                                                                             |         |

(Autonomous)

(ISO/IEC - 27001 - 2013 Certified)

#### WINTER-17 EXAMINATION

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### WINTER-17 EXAMINATION

Subject Name: BEM <u>Model Answer</u>

Subject Code: 17302

#### Working:

When Clk=1, the master J-K flip flop gets disabled. The Clk input of the master input will be the opposite of the slave input. So the master flip flop output will be recognized by the slave flip flop only when the Clk value becomes 0.

The circuit accepts the value in the input when the clock is HIGH, and passes the data to the output on the falling-edge of the clock signal.

#### Race around condition:

When J=k=1 output of Flip flop is toggles at each transition of clock. so it is just like race in '0' and '1'.

**Truth Table**

| J | K | CLK | Q                          |

|---|---|-----|----------------------------|

| 0 | 0 | t   | Q <sub>0</sub> (no change) |

| 1 | 0 | t   | 1                          |

| 0 | 1 | t   | 0                          |

| 1 | 1 | t   | $\overline{Q}_0$ (toggles) |

### e) What is Data logger? State applications of data logger (any 2)

#### Data logger:

A data logger, is an electronic instrument that records measurements of the instruments located at different parts of plant at set intervals over a period of time. Data logger measure and record data effortlessly as quickly, as often and as accurately desired.

#### **Applications: (any 2)**

- 1. power plant 2. Petrochemical plant 3. cement plant 4. AVCS

- 5. fertilizer industries 6. oil refinery 7. engine testing

02 marks for data logger 02 marks

for any correct applic ation

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### WINTER- 17 EXAMINATION

**Subject Name: BEM**

**Model Answer**

Subject Code: 17302

| f) | State the functions and applications of Robotics system (each two) | 02                                                      |

|----|--------------------------------------------------------------------|---------------------------------------------------------|

|    | Functions (any two):                                               | marks<br>for                                            |

|    | ✓ Metal cutting                                                    | functio<br>n                                            |

|    | ✓ Drilling                                                         |                                                         |

|    | ✓ System Assembly                                                  | 02<br>marks                                             |

|    | ✓ Component placing                                                | for applic                                              |

|    | Applications (any two): ✓ In Industry                              | ations                                                  |

|    | ✓ Domestic or household robots                                     |                                                         |

|    | ✓ Medical robots                                                   |                                                         |

|    | ✓ Service robots                                                   |                                                         |

|    | ✓ Military robots                                                  |                                                         |

| 6. | Any other correct functions and applications may be considered.    |                                                         |

|    | Attempt any four                                                   |                                                         |

|    | Draw LC filter with full wave rectifier. Also draw its waveform    |                                                         |

| a) | 230 V , 50Hz                                                       | 02<br>marks<br>for<br>circuit<br>02 for<br>wave<br>form |

(Autonomous)

(ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

Waveform: Output with filter Vdc Waveform Draw the circuit diagram of instrumentation amplifier using op-amp and label it. b) 04 marks. R2 R3 ٧2 INSTRUMENTATION AMPLIFIER

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### WINTER- 17 EXAMINATION

| Compare micrprocessor and micro  Microprocessor                                                                                                                                                                              | Microcontroller                                                                                                                                                                                                                                 | • |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1. Contains only CPU; RAM, ROM, I/O, timer are separately interfaced. 2. Designer decides on the amount of ROM, RAM and I/O ports. 3. High cost 4. General-purpose 5. High speed 6. Higher Power Consumption ex - 8085, 8086 | <ol> <li>CPU, RAM, ROM, I/O and timer are all on a single chip</li> <li>Fix amount of on-chip ROM, RAM, I/O ports</li> <li>Low cost</li> <li>Single-purpose</li> <li>Low speed</li> <li>Low Power Consumption</li> <li>ex - 8051,AVR</li> </ol> |   |

|                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 |   |

| 1) $A + B + C = Y$ A  B  C  C                                                                                                                                                                                                |                                                                                                                                                                                                                                                 |   |

| A<br>B<br>B                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                 |   |

#### WINTER- 17 EXAMINATION

Subject Name: BEM

Model Answer

Subject Code: 17302

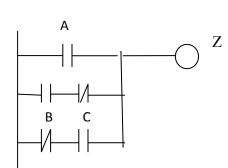

3)  $A + (B \oplus C) = Z$

02 Marks

e) Calculate the gain of inverting amplifier and non inverting amplifier if Rf= 10K  $\Omega$  , Ri=  $2K\Omega$

02 Marks

Gain of Inverting amplifier:

Gain Av = - Rf/Ri

=

$$-10K\Omega/2K\Omega$$

= -5

Negative sign indicate 180<sup>0</sup> phase shift

Gain of non Inverting amplifier :

Gain Av =

$$1 + Rf/Ri$$

=  $1 + 10K\Omega/2K\Omega$

=  $1 + 5$

=  $6$

02 Marks

Draw circuit of op amp as summing amplifier and obtain an expression for its output.

f) Working:

- Fig shows circuit diagram of op-amp as summing.

- Here the input voltages V1, V2, V3 are voltages applied to inverting terminal through Rin and Rf is the feedback register.

(Autonomous)

(ISO/IEC - 27001 - 2013 Certified)

#### **WINTER-17 EXAMINATION**

Subject Name: BEM <u>Model Answer</u> Subject Code: 17302

$V_1 \circ \overbrace{\hspace{1cm}}^{I_1} \stackrel{R_{in}}{\underset{V_2}{\overset{I_2}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}}{\overset{R_{in}}}{\overset{R_{in}}}{\overset{R_{in}}}}{\overset{R_{in}}}}{\overset{R_{in}}}{\overset{R_{in}}}$

- Apply KCL at node A, we will have

$$I1 + I2 + I3 = IB2 + If$$

$$I1 + I2 + I3 = If$$

----- (IB2 = 0, virtual ground concept) ---- (1)

- Consider the current flowing through the input resistors are

$$I_1 = \frac{V_1}{R},$$

$$I_2 = \frac{V_2}{R},$$

$$I_3 = \frac{V_3}{R}$$

the current through Rf is given by Therefore equation 1 became  $I_{\mathbf{f}} = -\frac{Vo}{Rf}$

$$V1/Rin + V2/Rin + V3/Rin = -Vo/Rf$$

Or

$$Vo = - Rf/Rin (V1+V2+V3)$$

if Rf= Rin then above equation become

$$V_0 = -(V_1+V_2+V_3)$$

this is the equation of output of summing amplifier is negative sum of all inputs

marks for diagra m 02 marks for derivat

ion